## **User Guide PRD-09491**

# CGD1200HB2P-XM3 Gate Driver User Guide

### This document is prepared as a user guide to install and operate Wolfspeed® evaluation hardware.

All parts of this user guide are provided in English, and the Cautions are provided in English, Mandarin, and Japanese. If the end user of this board is not fluent in any of these languages, it is your responsibility to ensure that they understand the terms and conditions described in this document, including without limitation the hazards of and safe operating conditions for this board.

本文件中的所有内容均以英文书写,"注意"部分的内容以英文、中文和日语书写。作为本板子的终端用户,即使您不熟悉上述任何一种语言,您也应当确保正确理解本文件中的条款与条件,包括且不限于本板子的危险隐患以及安全操作条款。

当書類のすべての内容は英語で書きます。「注意点」の内容は英語、中国語、また日本語で書きます。当ボードの端末使用者は上記の言語が一つでもわからないなら、当端末使用者は当書類の条約と条件が理解できるのを確保すべきです。そして、当ボードの危険や安全に使用する条件を含み、また限りません。

**Note:** This Wolfspeed-designed evaluation hardware for Wolfspeed® components is a fragile, high-voltage, high-temperature power electronics system that is meant to be used as an evaluation tool in a lab setting and to be handled and operated by highly qualified technicians or engineers. When this hardware is not in use, it should be stored in an area that has a storage temperature ranging from -40° Celsius to 105° Celsius. If this hardware is transported, to avoid any damage to electronic components, special care should be taken during transportation to avoid damaging the board or its fragile components and the board should be transported carefully in an electrostatic discharge (ESD) bag, or with ESD or shorting protection that is the same as, or similar to, the protection that is or would be used by Wolfspeed when shipping this hardware. Please contact Wolfspeed at <a href="https://forum.wolfspeed.com/">https://forum.wolfspeed.com/</a> if you have any questions about the protection of this hardware during transportation (and please rely only on forum responses from responders identified as Wolfspeed employees). The hardware does not contain any hazardous substances, is not designed to meet any industrial, technical, or safety standards or classifications, and is not a production-qualified assembly.

注意:本样机(易碎、高压、高温电力电子系统)由Wolfspeed为评估其功率半导体产品而设计,用以作为在实验室环境下由专业的技术人员或工程师处理和使用的评估工具。本样机不使用时,应存储在-40℃~105℃温度范围的区域内;如需运输样机,运输过程中应该特别小心,避免损坏电路板等易碎组件,且电路板应妥善放置于防静电(ESD)包装袋中,或采用其他与Wolfspeed发货时相同或类似的防静电或短路保护措施。如果您对此硬件在运输之中的保护有任何疑问,请访问https://forum.wolfspeed.com/,联系Wolfspeed。本样机不含任何有害物质,但其设计并非设计用于符合任何工业、技术或安全标准或分类,也不是可用于生产的组件。

注:Wolfspeed®コンポーネント向けにWolfspeedが設計したこの評価用ハードウェアは、脆弱な高電圧・高温パワーエレクトロニクスシステムであり、ラボ環境での評価ツールとして使用され、高度な資格を有する技術者またはエンジニアによって取り扱われ、操作されることを意図しています。このハードウェアを使用しない場合は、保管温度範囲が- $40^{\circ}$ Cから $105^{\circ}$ Cの場所で保管してください。このハードウェアを輸送する場合は、電子部品の損傷を避けるため、基板やその脆弱なコンポーネントに損傷を与えないよう特別な注意を払う必要があります。また基板は静電気放電(ESD)袋で慎重に輸送するか、Wolfspeedがこのハードウェアを輸送する際に使用している、または使用するであろう保護と同等または類似のESD保護または短絡保護を施してください。ハードウェアの輸送中の保護に関するご質問は、https://forum.wolfspeed.com/までお問い合わせください(フォーラムの回答をご覧になる場合は、Wolfspeed従業員が回答者であることが明記された投稿のみを参考にしてください)。このハードウェアは有害物質を含んでいませんが、いかなる産業・技術・安全基準または分類に適合するように設計されておらず、本番環境に適したアセンブリでもありません。

#### **CAUTION**

PLEASE CAREFULLY REVIEW THE FOLLOWING PAGES, AS THEY CONTAIN IMPORTANT INFORMATION REGARDING THE HAZARDS AND SAFE OPERATING REQUIREMENTS RELATED TO THE HANDLING AND USE OF THIS BOARD.

DO NOT TOUCH THE BOARD WHEN IT IS ENERGIZED AND ALLOW THE BULK CAPACITORS TO COMPLETELY DISCHARGE PRIOR TO HANDLING THE BOARD. THERE CAN BE VERY HIGH VOLTAGES PRESENT ON THIS EVALUATION BOARD WHEN CONNECTED TO AN ELECTRICAL SOURCE, AND SOME COMPONENTS ON THIS BOARD CAN REACH TEMPERATURES ABOVE 50° CELSIUS. FURTHER, THESE CONDITIONS WILL CONTINUE FOR A SHORT TIME AFTER THE ELECTRICAL SOURCE IS DISCONNECTED UNTIL THE BULK CAPACITORS ARE FULLY DISCHARGED.

Please ensure that appropriate safety procedures are followed when operating this board, as any of the following can occur if you handle or use this board without following proper safety precautions:

#### DEATH ▲ SERIOUS INJURY ▲ ELECTROCUTION ▲ ELECTRICAL SHOCK ▲ ELECTRICAL BURNS ▲ SEVERE HEAT BURNS

You must read this document in its entirety before operating this board. It is not necessary for you to touch the board while it is energized. All test and measurement probes or attachments must be attached before the board is energized. You must never leave this board unattended or handle it when energized, and you must always ensure that all bulk capacitors have completely discharged prior to handling the board. Do not change the devices to be tested until the board is disconnected from the electrical source and the bulk capacitors have fully discharged.

#### 警告

请认真阅读以下内容,因为其中包含了处理和使用本板子有关的危险隐患和安全操作要求方面的重要信息。

请勿在通电情况下接触板子,在操作板子前应使大容量电容器的电荷完全释放。接通电源后,该评估板上通常会存在危险的高电压,板子上一些组件的温度可能超过50摄氏度。此外,移除电源后,上述情况可能会短时持续,直至大容量电容器电量完全释放。

操作板子时应确保遵守正确的安全规程,否则可能会出现下列危险:

#### 死亡 ▲ 严重伤害 ▲ 触电 ▲ 电击 ▲ 电灼伤 ▲ 严重的热烧伤

请在操作本板子前完整阅读本文件。通电时禁止接触板子。所有测试与测量探针或附件必须在板子通电前连接。通电时,禁止使板子处于无人看护状态,且禁止操作板子。必须确保在操作板子前,大容量电容器已释放了所有电量。只有在切断板子电源,且大容量电容器完全放电后,才可更换待测试器件。

#### 警告

ボードの使用、危険の対応、そして安全に操作する要求などの大切な情報を含むので、以下の内容をよく読んでください。

通電している時、ボードに接触するのは禁止です。ボードを処分する前に、大容量のコンデンサーで電力を完全に釈放すべきです。通電してから、ボードにひどく高い電圧が存在している可能性があります。ボードのモジュールの温度は50度以上になるかもしれません。また、電源を切った後、上記の状況がしばらく持続する可能性がありますので、大容量のコンデンサーで電力を完全に釈放するまで待ってください。

ボードを操作するとき、正確な安全ルールを守るのを確保すべきです。さもないと、以下の危険がある可能性があります:

### 死亡 ▲ 重症 ▲ 感電 ▲ 電撃 ▲ 電気の火傷 ▲ 厳しい火傷

当ボードを操作する前に、完全に当書類をよく読んでください。通電している時にボードに接触する必要がありません。通電する前に必ずすべての試験用のプローブあるいはアクセサリーをつないでください。通電している時に無人監視やボードを操作するのは禁止です。ボードを操作する前に、大容量のコンデンサーで電力を完全に釈放するのを必ず確保してください。ボードの電源を切った後、また大容量のコンデンサーで電力を完全に釈放した後、試験設備を取り換えることができます。

## **User Guide PRD-09491**

# **CGD1200HB2P-XM3 Gate Driver User Guide**

## **Contents**

| 1. Introduction                                   | 6  |

|---------------------------------------------------|----|

| 2. Design Features                                | 6  |

| 2.1 Maximum Operating Parameters                  | 7  |

| 2.2 Assembly                                      | 7  |

| 2.3 Electrical Characteristics                    | 8  |

| 2.4 Block Diagram                                 | 9  |

| 3. Inputs/Outputs                                 | 10 |

| 3.1 Input Connector                               | 11 |

| 3.1.1 Pinout                                      | 12 |

| 3.1.2 Signal Descriptions                         | 12 |

| 3.2 Output Connectors                             | 13 |

| 3.3 Thermistor Connector                          | 14 |

| 3.4 V+ Connector                                  | 15 |

| 3.5 Gate-to-Source Voltage Measurement Connectors | 15 |

| 3.6 Status Indicators                             | 16 |

| 4. Features                                       | 17 |

| 4.1 Independent Gate Resistors                    | 17 |

| 4.2 Differential Signaling                        | 18 |

| 4.3 Adjustable Output Voltages                    | 19 |

| 4.4 Faults / Protections                          | 21 |

| 4.4.1 Input Voltage Protection                    | 22 |

| 4.4.2 Undervoltage Lockout                        | 23 |

| 4.4.3 Overcurrent Fault                           | 23 |

| 4.4.4 Overcurrent Trip Level                      | 24 |

| 4.4.5 Miller Clamp                                | 26 |

| 4.4.6 Interlock Protection                        | 26 |

| 4.5 Soft Shutdown                                 | 27 |

| 4.6 Timing Definitions                            | 27 |

| 4.7 Thermistor Feedback            | 28 |

|------------------------------------|----|

| 4.8 Power Estimates                | 29 |

| Dimensions                         |    |

| Supporting Links and Tools         |    |

| 6.1 Evaluation Tools and Support   |    |

| 6.2 Dual Channel Gate Driver Board |    |

| 6.3 Application Notes              |    |

### 1. Introduction

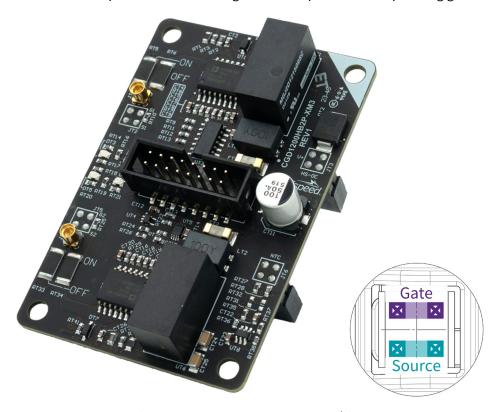

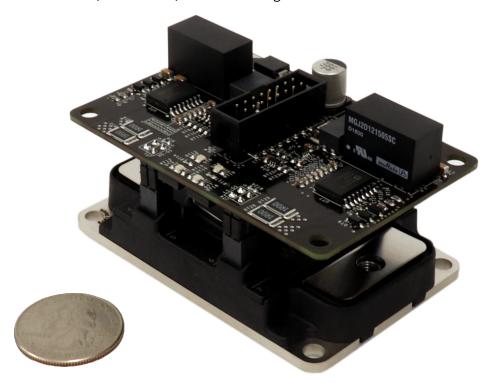

The CGD1200HB2P-XM3 gate driver, shown in Figure 1, is a dual channel isolated gate driver optimized for Wolfspeed's high-performance XM half-bridge power modules with the **inline gate pin configuration**. The gate driver is designed for high-frequency operation and can drive high-performance silicon carbide (SiC) power modules. It features separate 2 W isolated power supplies and Analog Devices® ADuM4146 gate drivers for independently operating the high- and low-side switch positions of a SiC power module. It is designed to attach directly to an XM power module and includes input voltage protection, differential inputs for increased noise immunity, soft shutdown, undervoltage lockout, and overcurrent protection. The CGD1200HB2P-XM3 design is intended to be an upgrade to the CGD12HBXMP gate driver by adding integrated gate measurement connections, improving the temperature feedback signaling, improving the overcurrent protection, and decreasing the soft-shutdown resistance for faster turn-off during faults. This user guide provides an overview of the gate driver functions and parameters including connector pinouts and operating guidance.

Figure 1: CGD1200HB2P-XM3 gate driver

## 2. Design Features

The CGD1200HB2P-XM3 gate driver is designed to operate at DC bus voltages up to 1500 V and includes system benefits such as onboard overcurrent, shoot-through protection, and reverse polarity protection. The maximum operating parameters of this gate driver design are shown in Table 1 and the full list of electrical parameters are shown in Table 2. Renderings of the board assembly from various views are shown in Figure 2.

## **2.1 Maximum Operating Parameters**

Table 1: Maximum operating parameters (verified by design)

| Parameter                                         | Symbol             | Value        | Unit |

|---------------------------------------------------|--------------------|--------------|------|

| Supply Voltage                                    | $V_{DC}$           | -0.5 to 13.2 | V    |

| Logic Level Input                                 | Vı                 | -0.5 to 5.5  |      |

| Output Peak Current (T <sub>A</sub> = 25 °C)      | Io                 | ±10          | А    |

| Output Power Per Channel (T <sub>A</sub> = 25 °C) | P <sub>DRIVE</sub> | 2            | W    |

| Maximum Switching Frequency                       | f                  | 80           | kHz  |

| (MOSFET Dependent, See Section 4.8)               | † <sub>SW</sub>    | 80           | KIIZ |

| Ambient Operating Temperature                     | T <sub>OP</sub>    | -40 to 85    | °C   |

| Storage Temperature                               | $T_{STG}$          | -40 to 85    | C    |

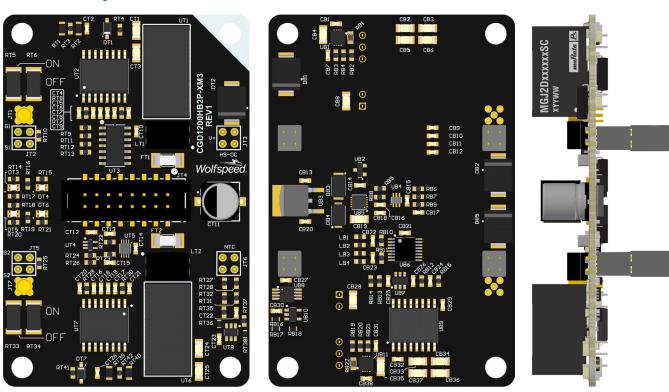

## 2.2 Assembly

Figure 2: CGD1200HB2P-XM3 rendering views

### 2.3 Electrical Characteristics

Table 2: Electrical characteristics (T = 25°C unless otherwise specified)

| Parameter                             | Symbol                      | Min. | Тур.  | Max. | Unit  | Test Conditions                                      |

|---------------------------------------|-----------------------------|------|-------|------|-------|------------------------------------------------------|

| Supply Voltage                        | $V_{DC}$                    | 10.8 | 12    | 13.2 |       |                                                      |

| Secondary Under Voltage Lockout       | $V_{UVLO}$                  |      | 11.5  | 12   |       |                                                      |

| Secondary UVLO Hysteresis             | $V_{HYS}$                   |      | 0.06  |      | •     |                                                      |

| Over Voltage Clamping                 | $V_{\text{OVLO}}$           | 18   | 20    | 22   | •     |                                                      |

| High Level Logic Input Voltage        | $V_{IH}$                    | 3.5  |       | 5.5  | •     | Single Ended Inputs                                  |

| Low Level Logic Input Voltage         | $V_{IL}$                    | 0    |       | 1.5  | •     | Single-Ended Inputs                                  |

| Diff Input Common Mode Range          | $V_{IDCM}$                  |      | ± 2.5 | ± 7  | •     | Differential Inputs                                  |

| Positive-going input threshold        | V <sub>IT+</sub>            |      |       | 0.2  | ٧     |                                                      |

| voltage, differential input           | V IT+                       |      |       | 0.2  |       | $V_{ID} = V_{POS-LINE} - V_{NEG-LINE}$               |

| Negative-going input threshold        | V <sub>IT-</sub>            | -0.2 |       |      | •     | VID — VPOS-LINE — VNEG-LINE                          |

| voltage, differential input           | V <sub>IT</sub> -           | -0.2 |       |      |       |                                                      |

| Differential Output Magnitude         | $V_{\text{OD}}$             | 2    | 3.7   |      |       | R <sub>L</sub> = 100 Ω                               |

| High level Output Voltage             | $V_{GATE,HIGH}$             |      | +15   |      |       |                                                      |

| Low level Output Voltage              | $V_{GATE,LOW}$              |      | -4    |      |       |                                                      |

| Working Isolation Voltage             | $V_{IOWM}$                  |      | 1500  |      |       | V <sub>RMS</sub>                                     |

| Isolation Capacitance                 | C <sub>ISO</sub>            |      | 4.9   |      | pF    | Per Channel                                          |

| Common Mode Transient Immunity        | CMTI                        | 100  |       |      | kV/μs | V <sub>CM</sub> = 1500 V                             |

| Output Resistance <sup>1</sup>        | R <sub>G(IC)-ON</sub>       |      | 0.48  | 0.98 |       | Gate Driver Buffer Tested                            |

| Output Resistance                     | R <sub>G(IC)-OFF</sub>      |      | 0.47  | 0.81 | Ω     | at 1 A                                               |

| External Resistance <sup>2</sup>      | R <sub>G(EXT)-ON</sub>      |      | 1     |      | 12    | External SMD Resistor                                |

| External Resistance                   | R <sub>G(EXT)-OFF</sub>     |      | 1     |      | •     | 2512 (6432 Metric)                                   |

| Output Rise Time                      | t <sub>on</sub>             |      | 223   |      |       | $R_{G(EXT)} = 1 \Omega$ , $C_{LOAD} = 47 \text{ nF}$ |

| Output Fall Time                      | t <sub>OFF</sub>            |      | 208   |      | •     | From 10% to 90%                                      |

| Propagation Delay (Turn-Off)          | $t_{\scriptscriptstylePHL}$ |      | 120   |      | ns    | $R_{G(EXT)} = 1 \Omega$ , $C_{LOAD} = 0 nF$          |

| Propagation Delay (Turn-On)           | $t_{\scriptscriptstylePLH}$ |      | 125   |      | •     | From 50% to 50%                                      |

| Over-current Blanking Time            | t <sub>BLANK</sub>          |      | 600   |      | •     | $R_{G(EXT)} = 1 \Omega$ , $C_{LOAD} = 47 \text{ nF}$ |

| Over-current Propagation Delay to     | _                           |      | 1 2   |      |       | Does Not Include                                     |

| FAULT Signal Low                      | t <sub>PD-FAULT</sub>       |      | 1.3   |      | μs    | Blanking                                             |

| Soft-Shutdown Time                    | t <sub>ss</sub>             |      | 1.3   |      |       | $R_{G(EXT)} = 1 \Omega$ , $C_{LOAD} = 47 \text{ nF}$ |

| Soft-Shutdown Resistance <sup>3</sup> | R <sub>ss</sub>             |      | 5     |      | 0     | Tested at 25 mA                                      |

| Miller Clamp Resistance               | R <sub>MC</sub>             |      | 1.1   | 2.75 | Ω     | Tested at 100 mA                                     |

| Miller Clamp Voltage Threshold        | $V_{MC}$                    | 1.75 | 2     | 2.25 | ٧     | Reference to Source                                  |

<sup>&</sup>lt;sup>1</sup> Output resistance of gate driver integrated circuit (IC).

<sup>&</sup>lt;sup>2</sup> Additional output resistance is added with surface mount device (SMD) resistors. Separate resistors allowing independent tuning.

<sup>&</sup>lt;sup>3</sup> Soft-shutdown network will safely turn off the gate if an over-current event is detected.

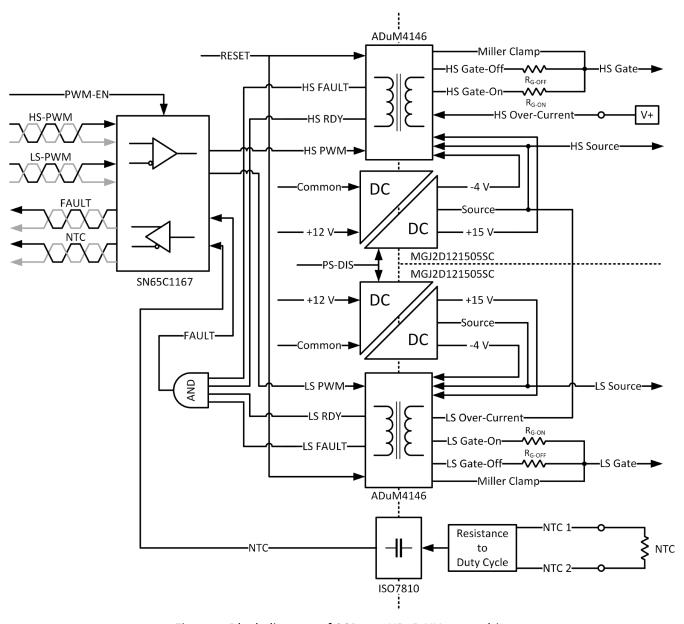

## 2.4 Block Diagram

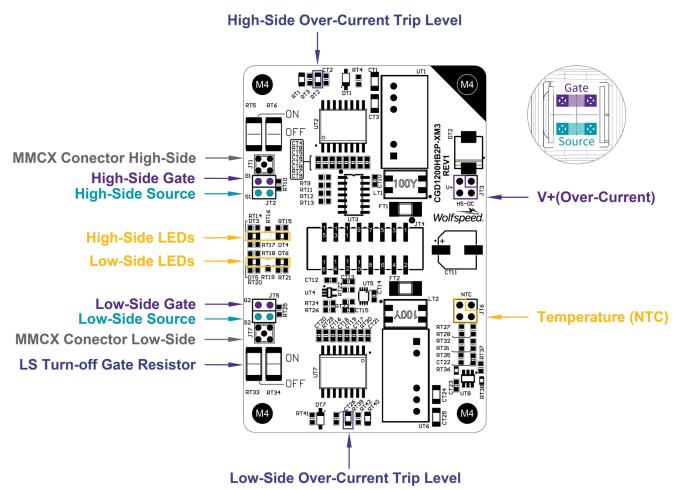

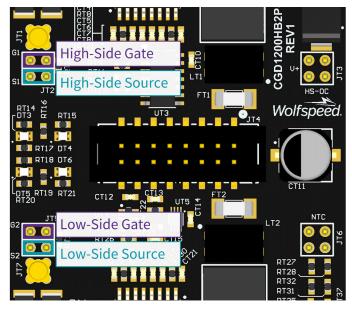

A block diagram of the full gate driver is shown in Figure 3. Both channels (high- and low-side) include a dedicated isolated DC/DC converter and gate driver integrated circuit (IC) for independent modulation of the respective channel. The gate driver communicates with a controller via differential signaling for both input and feedback signals. The gate driver combines all onboard fault signals (i.e. overcurrent and power faults for both channels) into a single global fault signal which is transmitted to the controller to indicate the board status. The board includes an overcurrent detection circuit, independent turn-on and turn-off resistors, Miller clamp, and thermistor feedback. Some notable interface features on the board are indicated in Figure 4.

Figure 3: Block diagram of CGD1200HB2P-XM3 gate driver

Figure 4: Interface of CGD1200HB2P-XM3 gate driver

## 3. Inputs/Outputs

The CGD1200HB2P-XM3 gate driver includes multiple connectors for interfacing with the power module and control signals and to perform measurements. This section details the pinout and functionality of each of these connectors. An overview of the purpose of each connector is shown in Table 3 along with the corresponding document section to find additional information.

| Ref. Des. Side          |                                       | Description                           | Section |

|-------------------------|---------------------------------------|---------------------------------------|---------|

| JT1                     | Тор                                   | High-side V <sub>GS</sub> measurement | 3.5     |

| JT2                     | Bottom                                | High-side output                      | 3.2     |

| JT3                     | JT3 Bottom V+ measurement             |                                       | 3.4     |

| JT4                     | Тор                                   | Input signals                         | 3.1     |

| JT5 Bottom Low-side out |                                       | Low-side output                       | 3.2     |

| JT6                     | <b>JT6</b> Bottom Thermistor feedback |                                       | 3.3     |

| JT7                     | Тор                                   | Low-side V <sub>GS</sub> measurement  | 3.5     |

Table 3: Summary of input/output connectors

### 3.1 Input Connector

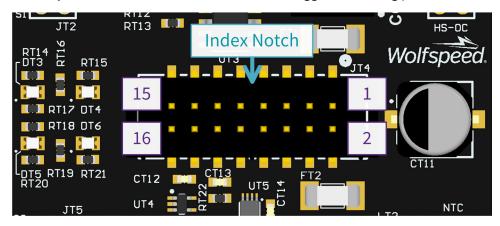

The CGD1200HB2P-XM3 gate driver is intended to operate with differential signaling for improved noise immunity compared to single-ended signaling (see Section 4.2). All the control and feedback signals with this gate driver are digital and interface through a single input connector (reference designator *JT4*). This connector orientation and the corresponding pin locations are shown in Figure 5. *JT4* uses part number SBH11-NBPC-D08-SM-BK manufactured by Sullins Connector Solutions and the suggested mating parts are listed in Table 4.

Figure 5: JT4 input connector orientation and pin locations

Table 4: Input connector suggested mating parts

| Component          | Manufacturer             | Part Number   | Description                              |

|--------------------|--------------------------|---------------|------------------------------------------|

| Mating IDC         | <b>Sullins Connector</b> | SBH11-NBPC-   | 16 Position Rectangular Header Connector |

| Connector          | Solutions                | D08-SM-BK     | IDC Gold 28 AWG                          |

| Straight Ribbon    | 21/1                     | HF365/16SF    | Flat Ribbon Cable Gray 16 Conductors     |

| Cable <sup>1</sup> | Cable <sup>1</sup> 3M    |               | 0.050" (1.27mm) Flat Cable               |

| Twisted Ribbon     | 21/4                     | 1700/16 100SF | Flat Ribbon Cable Multiple 16 (8 Pair    |

| Cable <sup>1</sup> | Cable <sup>1</sup> 3M    |               | Twisted) Conductors 0.050" (1.27mm)      |

| Mating Vertical    | Sullins Connector        | SFH11-PBPC-   | 16 Position Header Connector 0.100"      |

| (PCB Mount)        | Solutions                | D08-ST-BK     | (2.54mm) Through Hole Gold               |

| Mating Right-Angle | Sullins Connector        | SFH11-PBPC-   | 16 Position Header Connector 0.100"      |

| (PCB Mount)        | Solutions                | D08-RA-BK     | (2.54mm) Through Hole, Right Angle Gold  |

<sup>&</sup>lt;sup>1</sup> When using ribbon cable for long connections, it is recommended to use twisted-pair ribbon cable for improved noise immunity.

#### **3.1.1 Pinout**

Table 5: Pinout of JT4 input connector

| Pin         | Name        | Description                                                                            |

|-------------|-------------|----------------------------------------------------------------------------------------|

| 1           | VDC         | Power supply input pin (+12 V Nominal Input).                                          |

| 2           | Common      | Common.                                                                                |

| 3           | HS-PWM-P*   | Positive line of 5 V differential high-side PWM signal pair. Terminated into 120 Ω.    |

| 4           | HS-PWM-N*   | Negative line of 5 V differential high-side PWM signal pair. Terminated into 120 Ω.    |

| 5           | LS-PWM-P*   | Positive line of 5 V differential low-side PWM signal pair. Terminated into 120 Ω.     |

| 6           | LS-PWM-N*   | Negative line of 5 V differential low-side PWM signal pair. Terminated into 120 Ω.     |

|             |             | Positive line of 5 V differential fault condition signal pair. Drive strength 20 mA. A |

| 7           | FAULT-P*    | low state on FAULT indicates when a desaturation fault has occurred. The presence      |

|             |             | of a fault precludes the gate drive output from going high.                            |

| 8           | FAULT-N*    | Negative line of 5 V differential fault condition signal pair. Drive strength 20 mA.   |

| 9           | THERM-P*    | Positive line of 5 V temperature dependent resistor output signal pair. Drive          |

| 9           | I MEKIVI-P  | strength 20 mA. Temperature measurement is encoded via duty cycle.                     |

| 10 THERM-N* |             | Negative line of 5 V temperature dependent resistor output signal pair. Drive          |

| 10          | TTTLKW-N    | strength 20 mA. Temperature measurement is encoded via duty cycle.                     |

| 11          | PS-DIS      | Pull down to disable power supply. Pull up or leave floating to enable. Gate and       |

| 11          | . 43-013    | source are connected with 10 kΩ when disabled.                                         |

| 12          | Common      | Common.                                                                                |

| 13          | PWM-EN      | Pull down to disable PWM input logic. Pull up or leave floating to enable. Gate driver |

| 13          | E AAIAI-FIA | output will be held low through turn-off gate resistor if power supplies are enabled.  |

| 14          | Common      | Common.                                                                                |

| 15          | Reset       | When a fault exists, bring this pin high for >500 ns to clear the fault.               |

| 16          | Common      | Common.                                                                                |

<sup>\*</sup> Inputs 3-10 are differential pairs.

### 3.1.2 Signal Descriptions

*PWM Signals*: High-side and low-side pulse-width modulation (PWM) signals are RS-422 compatible differential inputs. The termination impedance of the differential receiver is 120  $\Omega$ . Overlap protection is provided to prevent both the high-side and low-side gates from turning on simultaneously. The overlap protection should not be used as a dead time generator.

FAULT Signal: The fault signal is a RS-422 compatible differential output with a maximum drive strength of 20 mA. A high signal (positive line > negative line) means there are no fault conditions for either gate driver channel. This signal will be low if an overcurrent fault or undervoltage-lockout (UVLO) fault condition is detected on either channel. The onboard light-emitting diodes (LEDs) will indicate the fault condition. See Sections 3.6 and 4.4 for more details.

THERM Signal: THERM output is a differential signal that returns the resistance of the temperature sensor integrated into XM modules. It is a duty cycle signal that encodes the resistance of the temperature sensor.

The approximate temperature of the module can be determined from this resistance. See the Section 4.7 for further details.

$\overline{\textit{PS-DIS}}$ : The PS-DIS signal disables the output of the isolated DC/DC converters for the two channels. It is a single-ended input that must be pulled low to turn off the power supplies. With the power supplies disabled the gate will be held low with a 10 k $\Omega$  resistor. This signal can be used for startup sequencing.

PWM-EN: This is a single-ended input that enables the PWM inputs for both channels. When this signal is pulled down the differential receivers for both channels are disabled, and the gates will both be pulled low through  $R_{G(EXT)$ -OFF. All protection circuitry and power supplies will continue to operate including FAULT and THERM outputs.

*RESET*: This is a single-ended input that can be used to clear overcurrent faults on the gate driver. To clear an overcurrent fault, this signal must be commanded high for at least 500 ns. While the signal remains high, the outputs of the gate driver remain disabled. On the gate driver board, this input is held low with a 10 k $\Omega$  resistor. This signal resets both channels of the gate driver.

### 3.2 Output Connectors

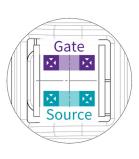

The output connectors on the CGD1200HB2P-XM3 gate driver are four pin headers designed to attach directly to the XM power modules with inline gate pins. An example connection is shown in Figure 6. The power bussing connects directly to the power terminals of the module. **The CGD1200HB2P-XM3 gate driver should not be used on XM power modules with crossed gate pins** (see PRD-07128). The high-side and low-side output connectors are isolated from each other and do not share a source connection. The gate and source connections for both channels, *JT2* and *JT5*, are shown in Figure 7.

Figure 6: Example gate driver attached to XM power module

Figure 7: JT2 and JT5 output connectors orientations and pin locations

### 3.3 Thermistor Connector

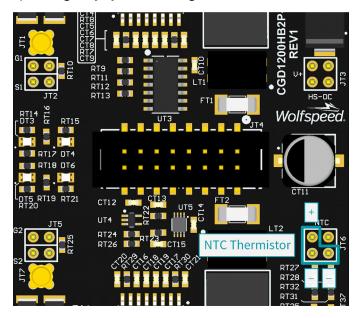

The XM power modules include an integrated negative temperature coefficient (NTC) thermistor for monitoring the baseplate temperature of the module (see <u>PRD-08376</u>). The CGD1200HB2P-XM3 gate driver includes circuitry to directly measure this thermistor and encode the resistance as a duty cycle to the controller. The thermistor connector, *JT6*, attaches directly to the XM module and is shown in Figure 8. Two pins of the connector are attached to one side of the thermistor (shown as "-" in the figure) and one pin is attached to the other side of the thermistor (shown as "+" in the figure). See Section 4.7 for more information about the thermistor circuit and corresponding duty cycle encoding.

Figure 8: JT6 thermistor connector orientation and pin locations

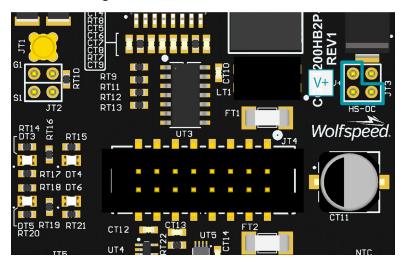

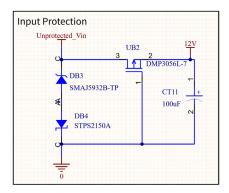

### 3.4 V+ Connector

The desaturation circuit employed on this design for overcurrent protection (see Section 4.4.3) requires accurate feedback of the MOSFET drain terminals to identify when the module is conducting elevated current. For overcurrent protection of the low-side switch position, the desaturation circuit can directly measure the high-side source terminal on the gate driver to determine the drain voltage of the low-side position. For overcurrent protection of the high-side switch position, the XM power module family provides access to the high-side drain terminal through a dedicated connector. The CGD1200HB2P-XM3 gate driver includes a connector, *JT3*, to access the high-side drain terminal for overcurrent protection. This connector, shown in Figure 9, engages with the XM module the same as the output connectors and thermistor connector. All the pins of the connector are attached to the high-side drain terminal.

Figure 9: JT3 V+ connector orientation and pin locations

This connector cannot be left floating as the overcurrent fault will trip immediately when the high-side gate is actuated. If bench-top testing of the gate driver is required, it is acceptable to short this connector to the high-side source to prevent the overcurrent fault from tripping.

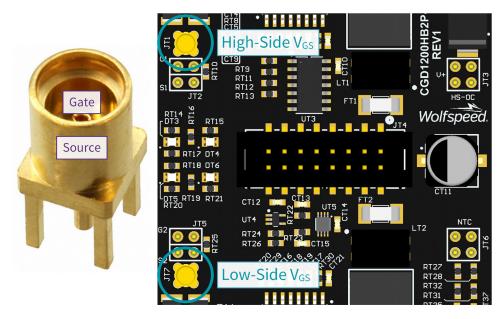

## **3.5 Gate-to-Source Voltage Measurement Connectors**

A high-fidelity gate-to-source voltage measurement (V<sub>GS</sub>) is critical for many applications such as device characterization, system commissioning, and troubleshooting. The CGD1200HB2P-XM3 gate driver includes integrated micro-miniature coaxial (MMCX) connectors for measuring the V<sub>GS</sub> outputs of the gate driver. The pinouts and locations for the measurement connectors are shown in Figure 10. A variety of probes can interface directly with these standard MMCX connectors. Wolfspeed recommends performing these measurements with an optically isolated probe such as the Tektronix® IsoVu<sup>TM</sup> series of probes to ensure high common-mode rejection during measurements. This is especially critical for the high-side V<sub>GS</sub> measurement which is referenced to a varying voltage node. If this gate driver board is attached to the device under test through an interface board (i.e. the board is not directly attached to the power module), it is recommended to measure the gate-to-source voltage on the interface board rather than on this gate driver to ensure a high-fidelity measurement.

Figure 10: JT1 and JT7 measurement connectors orientations and pin locations

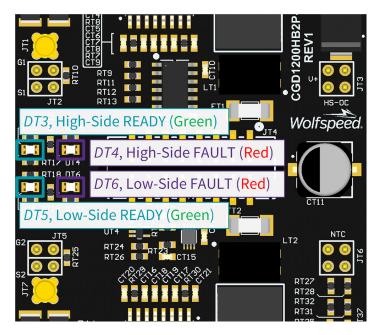

### 3.6 Status Indicators

The CGD1200HB2P-XM3 gate driver includes four LEDs, shown in Figure 11, to indicate the state of the board. The functionality of these LEDs is summarized in Table 6. In normal operation, the green READY LEDs (*DT3* and *DT5*) will be illuminated, indicating that the gate driver board is functioning as expected. When the system faults due to an overcurrent event, the channel(s) where the fault occurred will illuminate the corresponding red FAULT LED (*DT4* and/or *DT6*). When the gate driver has an UVLO or thermal shutdown (TSD) event, the READY LED of the relevant channel(s) will be extinguished. The status of the gate driver board depending on the LED states is summarized in Table 7.

Figure 11: Status LEDs: locations and purposes

Table 6: Status LED descriptions

| LED | Color | Description     |

|-----|-------|-----------------|

| DT3 | Green | High-Side READY |

| DT4 | Red   | High-Side FAULT |

| DT5 | Green | Low-Side READY  |

| DT6 | Red   | Low-Side FAULT  |

Table 7: Status LED states

| READY LED<br>(DT3   DT5) | FAULT LED<br>( <i>DT4</i>   <i>DT6</i> ) | Description                                                     |

|--------------------------|------------------------------------------|-----------------------------------------------------------------|

| 1                        | 0                                        | Normal operation. No issues.                                    |

| 0                        | Х                                        | Bad power rail(s) or thermal shutdown. Check input power        |

| U                        | ^                                        | quality, fuses, component failure, and output short-circuit.    |

| Х                        | 1                                        | Overcurrent fault. Clear fault condition and reset gate driver. |

1 = LED On | 0 = LED Off | X = Irrelevant

### 4. Features

The CGD1200HB2P-XM3 gate driver includes several design features intended to enable it to efficiently and reliably drive high-performance SiC MOSFETs at high frequencies. These features – which enable higher efficiency, noise immunity, flexibility, and protection – are detailed in this section.

## **4.1 Independent Gate Resistors**

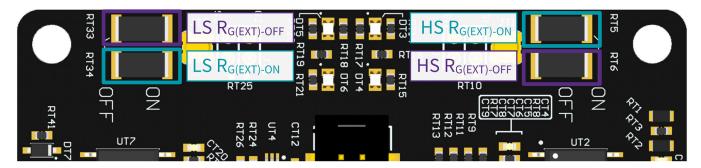

The design includes separate external turn-on and turn-off resistors for both channels of the gate driver. The different resistors allow for independent tuning of the turn-on and turn-off switching dynamics. This can be useful for optimizing switching losses while staying within the safe operating bounds. By default, the CGD1200HB2P-XM3 gate driver includes  $1\,\Omega$  gate resistors for turn-off and turn-on for both channels, though the resistors can be easily changed to adjust the switching dynamics. The default resistors used are Vishay Dale CRCW25121R00FKEGHP resistors in a surface-mount 2512 (6432 metric) footprint. In an effort to maximize performance, it is recommended to use pulse-rated resistors when replacing/changing the gate resistors. The locations of the gate resistors are shown in Figure 12, and the purpose of each resistor is summarized in Table 8. See PRD-09301 for more information about independent gate resistor tuning.

Figure 12: External turn-on and turn-off gate resistor locations

Table 8: External gate resistors descriptions

| Ref. Des.                                 | Ref. Des. Default Description |                                      |  |  |

|-------------------------------------------|-------------------------------|--------------------------------------|--|--|

| <b>RT5</b> 1 Ω High-Side External Turn-On |                               | High-Side External Turn-On Resistor  |  |  |

| <b>RT6</b> 1 Ω                            |                               | High-Side External Turn-Off Resistor |  |  |

| <b>RT33</b> 1 Ω Lo                        |                               | Low-Side External Turn-Off Resistor  |  |  |

| <b>RT34</b> 1 Ω                           |                               | Low-Side External Turn-On Resistor   |  |  |

## **4.2 Differential Signaling**

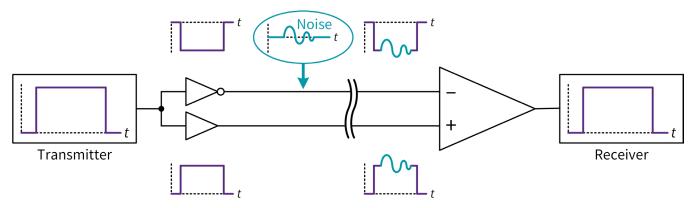

Signal integrity is critical when controlling power devices with a gate driver. A gate driver that is susceptible to the powerful interference generated by power devices can induce a shoot-through condition in the module. The extremely fast turn-on and turn-off times during the switching events in a SiC power system can create electromagnetic interference (EMI) that can easily couple onto the gate control signals. For this reason, differential signaling was adopted instead of standard, single-ended connections between the gate driver and control board. More information about differential signaling compared to single-ended connections is provided in PRD-09301.

Differential signaling significantly reduces the impact of radiated noise from the switching events of a power module. A single-ended signal can be converted to a differential signal by transmitting both the original signal and its complement in two closely coupled wires. At the receiver, the two signals are compared in order to reconstruct the original signal. Figure 13 illustrates this principle with an example of induced noise forced onto the cable somewhere between the transmitter and receiver. The noise affects both the original signal and the complement by the same magnitude assuming that the cables are consistently coupled. Thus, when the receiver compares the two signals, the difference is unaffected by the noise induced on the line and the intended original signal is created.

Figure 13: Noise immunity improvement provided by differential signaling

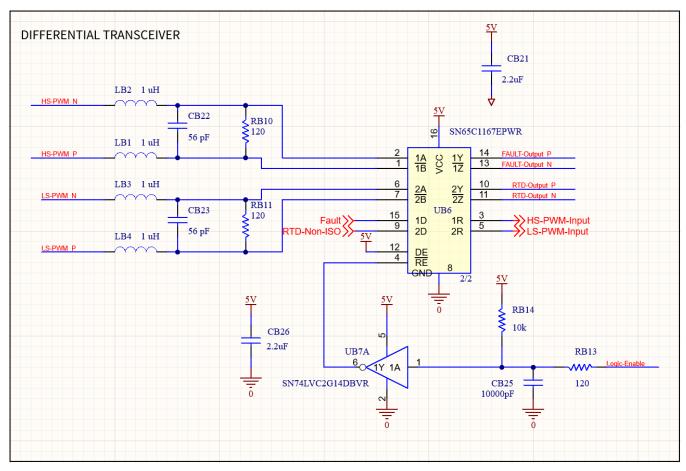

The CGD1200HB2P-XM3 gate driver requires differential communication for proper performance. This can be achieved through differential transceivers included directly on a control board or using a single-ended to differential transceiver board. Wolfspeed provides the <a href="CGD12HB00D">CGD12HB00D</a> 2-channel differential transceiver companion tool for adding differential signaling to projects. For a reference design which adds differential

transceivers to the control board, see the control board design from the <u>CRD300DA12E-XM3</u> inverter. The differential circuit implemented on the CGD1200HB2P-XM3 gate driver board is shown in Figure 14.

Figure 14: Differential signaling circuit

## **4.3 Adjustable Output Voltages**

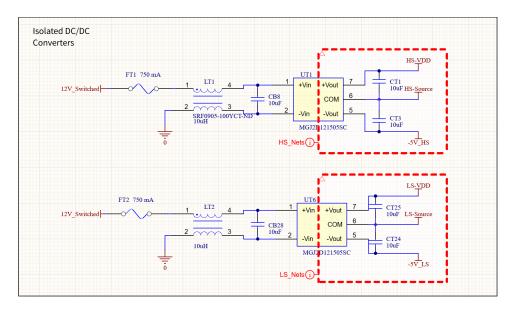

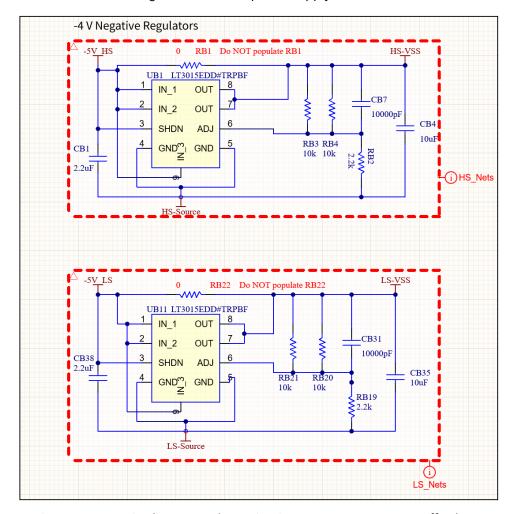

By default, the gate driver outputs a high voltage of +15 V and a low voltage of -4 V. The default onboard isolated power supply directly generates +15 V and -5 V rails (Figure 15), and an onboard linear regulator is employed to reduce the output-low voltage from -5 V to -4 V (Figure 16). These voltages can be manipulated to characterize and/or operate the SiC power module under different bias conditions.

Figure 15: Isolated power supply circuits

Figure 16: Negative linear regulator circuits to generate -4 V turn-off voltage

To change the turn-off voltage, change the feedback resistor network on the linear regulator to adjust the voltage using the equation below. The output voltage of the linear regulator can be adjusted between -1.22 V and ( $V_{IN}$  + 0.3 V). The linear regulator can also be bypassed by removing the linear regulator and populating the unpopulated 0  $\Omega$  resistors on the board (*RB1* and *RB22*).

$$V_{OUT} = -1.22 V \left(1 + \frac{R_2}{R_1}\right) + (I_{ADJ})(R_2)$$

where

$R_1$ : bias resistor attached to the common rail  $[\Omega]$

$R_2$ : bias resistor attached the output voltage rail  $[\Omega]$

$I_{ADJ}$ : bias current (30 nA at 25 °C, see component datasheet for more information) [A]

The calculation for the default circuit configuration of -4 V is shown below for reference.

$$-1.22 V \left(1 + \frac{5 k\Omega}{2.2 k\Omega}\right) + (30 nA)(5 k\Omega) = -4 V$$

To adjust the output-high voltage (or as an alternative method to change the output-low voltage), simply swap the isolated power supply on the board. The isolated power supply used on the board uses an industry-standard 5-pin 7-SIP footprint, so many manufacturers have solutions with different output voltages. Note that the power supply is critical to maintaining high isolation on the gate driver board. If changing the isolated power supply, ensure that it has suitable isolation ratings for the intended application.

The power modules are not intended to be operated continuously in the linear region, so the user should ensure that the selected voltages are within the safe operating area of the device. Also, the overcurrent protection circuit trip point is biased from the output-high voltage rail (see Section 4.4.4), so modifying this voltage can influence the trip point of the overcurrent protection circuit. Furthermore, the digital isolator used for the thermistor feedback circuit (see Section 4.7) is powered from the gate driver output-low voltage rail. Configuring the output-low voltage rail too low could lose operation of the thermistor feedback circuit. Careful scrutiny should be employed if the power rails are being modified.

## 4.4 Faults / Protections

The CGD1200HB2P-XM3 gate driver is protected from input +12 V power quality issues, isolated power supply issues, signal overlap, and overcurrent events in the power module. This section discusses these faults in more detail and how to adjust them. Table 9 provides a logic table summary indicating the state of the gate driver outputs depending on the various input signals and/or fault statuses.

|     |        | Overcurrent/ |       |      |       |        |

|-----|--------|--------------|-------|------|-------|--------|

| PWM | PWM-EN | PS-DIS       | RESET | UVLO | FAULT | Output |

| Н   | H or Z | H or Z       | L     | No   | Н     | Н      |

| L   | H or Z | H or Z       | L     | No   | Н     | L      |

| Х   | L      | H or Z       | L     | No   | Н     | L      |

| Х   | Х      | L            | Х     | No   | L     | Z      |

| Х   | H or Z | H or Z       | L     | Yes  | L     | L      |

Table 9: Output logic table depending on inputs and faults

$H = High \mid L = Low \mid X = Irrelevant \mid Z = High Impedance$

### 4.4.1 Input Voltage Protection

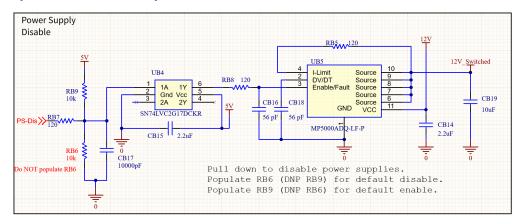

The CGD1200HB2P-XM3 gate driver includes overvoltage, inrush current, and reverse voltage protection on the +12 V power input (pin 1) of the input connector, *JT4*. The inrush current protection is implemented through a power management circuit, shown in Figure 17, which can be enabled/disabled through the *PS-DIS* signal to remotely handle start-up sequencing. The implemented overvoltage and reverse voltage protection circuit is shown in Figure 18. The Zener diode protects from input voltage spikes greater than 20 V (nominal) and the P-channel MOSFET protects from the positive and negative polarities being reversed. Incorrect connections should be avoided when using the CGD1200HB2P-XM3 gate driver, although these circuit elements are included to protect the system if it is incorrectly wired.

Figure 17: Input overcurrent protection and power disable circuit

Figure 18: Input overvoltage and reverse voltage protection circuit

### 4.4.2 Undervoltage Lockout

The Analog Devices ADuM4146C gate driver IC used on this design features integrated UVLO. The UVLO circuit detects when the output rails of the isolated DC/DC converter fall below safe operating conditions for the gate driver. A UVLO fault indicates that the potential between the split output voltage rails has fallen below the UVLO active level. The gate for the channel where the fault occurred will be pulled low through  $R_{G(EXT)-OFF}$  for the duration of the fault regardless of the PWM input signal. The fault will automatically clear once the potential has risen above the UVLO inactive level. There is hysteresis for this fault to ensure safe operating conditions. The UVLO faults for both channels are combined along with the overcurrent fault in the FAULT output signal. When there is no UVLO fault present, a green LED indicates a power good state. The LED, DT3, indicates a high-side power good status, and DT5 indicates a low-side power good status.

### **4.4.3 Overcurrent Fault**

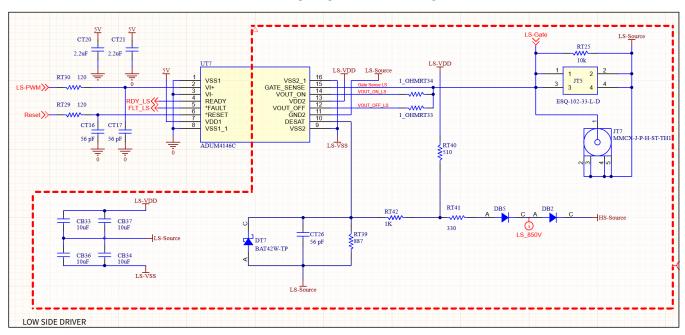

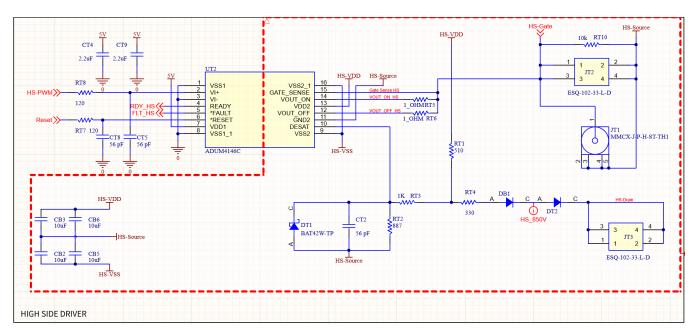

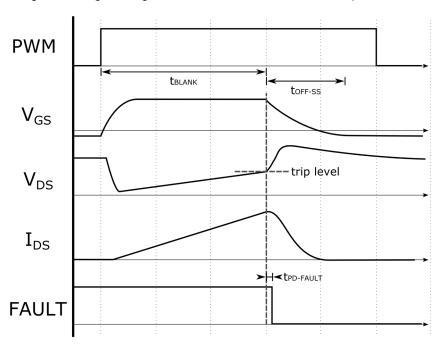

An overcurrent (OC) fault is an indication of an overcurrent event in the SiC power module. The overcurrent protection circuit, shown in Figure 19 for the low-side and in Figure 20 for the high-side, measures the drain-to-source voltage (V<sub>DS</sub>), and the fault will indicate if this voltage has risen above a level corresponding to the safe current limit. When a fault has occurred, the corresponding gate driver channel will be disabled, and the gate will be pulled down through a soft-shutdown resistance, R<sub>SS</sub>. The drain-source limit can be configured through onboard resistors. The overcurrent fault is latched upon detection and must be cleared by the user with a high pulse of at least 500 ns on the *RESET* signal. The various timing and voltage trip levels presented in Table 2 and Section 4.4.4 are defined notionally in the timing diagram shown in Figure 21.

Figure 19: Low-side gate driver circuit with overcurrent protection

Figure 20: High-side gate driver circuit with overcurrent protection

Figure 21: Overcurrent fault timing diagram

### 4.4.4 Overcurrent Trip Level

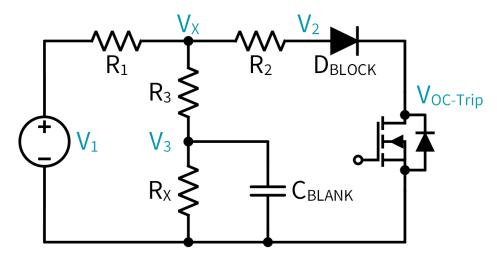

The OC fault detection circuit, shown in Figure 19 and Figure 20, measures the on-state  $V_{DS}$  across each switch position and triggers a fault condition if the voltage rises above the predefined set level. The circuit is simplified into the notional diagram shown in Figure 22. Referring to this figure, the intermediary voltages  $V_2$  and  $V_X$  and the trip resistor,  $R_X$ , can be calculated using the following equations:

Figure 22: Notional overcurrent fault circuit

$$V_2 = V_{OC-Trip} + N_D \cdot V_F \; ; \; V_X = \frac{R_2 R_3 V_1 + R_1 R_3 V_2 + R_1 R_2 V_3}{R_1 R_2 + R_1 R_3 + R_2 R_3} \; ; \; R_X = \frac{V_3 \cdot R_3}{V_X - V_3}$$

where

$V_2$ : intermediate voltage shown in Figure 22 [V]

$V_{OC-Trip}$ : target overcurrent trip voltage [V]

$N_D$ : number of series high-voltage blocking diodes

$V_F$ : forward voltage of the high-voltage blocking diode(s) [V]

$V_X$ : intermediate voltage shown in Figure 22 [V]

$V_1$ : source voltage (output-high gate driver voltage) [V]

$V_3$ : internal comparator trip voltage of the gate driver IC [V]

$R_1, R_2, R_3$ : circuit resistor values  $[\Omega]$

$R_X$ : resistor value required to trip at the appropriate overcurrent value  $[\Omega]$ .

To select an appropriate overcurrent trip level, refer to the  $I_D$  vs.  $V_{DS}$  output characteristic curves in the applicable module datasheet. As an example, the pulse-current rating of Wolfspeed's CAB450M12XM3 is 900 A; therefore, an overcurrent trip point of 1000 A at 25 °C is selected. On the  $I_D$  vs.  $V_{DS}$  curve, the drain-to-source voltage at the 1000 A operating condition is approximately 2.9 V. Hence, the over-current trip voltage,  $V_{OC-Trip}$ , should be approximately 2.9 V. Using this value and with the values from the schematic (shown below), the necessary trip resistor,  $R_X$ , can be calculated, as shown below.

$V_{OC-Trip}$ : 2.9 V (from the datasheet I<sub>D</sub> vs V<sub>DS</sub> plot of the example module)

$N_D$ : 2 (from gate driver schematic)

$V_F$ : 0.5 (from high-voltage diode datasheet)

$V_1$ : 15 V (from gate driver schematic)

$V_3$ : 3.5 V (from the Analog Device ADuM4146C datasheet)

$R_1$ : 510  $\Omega$ ;  $R_2$ : 330  $\Omega$ ;  $R_3$ : 1 k $\Omega$  (from gate driver schematic)

$$V_2 = 2.9 V + 2 * 0.5 V \rightarrow V_2 = 3.9 V$$

$$V_x = \frac{330 \ \Omega * 1000 \ \Omega * 15 \ V + 510 \ \Omega * 1000 \ \Omega * 3.9 \ V + 510 \ \Omega * 330 \ \Omega * 3.5 V}{510 \ \Omega * 330 \ \Omega + 510 \ \Omega * 1000 \ \Omega + 330 \ \Omega * 1000 \ \Omega} \rightarrow V_x = \ \textbf{7.466} \ V$$

$$R_x = \frac{3.5 \ V * 1000 \ \Omega}{7.466 \ V - 3.5 \ V} = \frac{3500}{3.966} \rightarrow \ \textbf{R}_x = \textbf{883} \ \Omega$$

By default, the CGD1200HB2P-XM3 gate driver is configured with a 2.9 V overcurrent trip voltage, and therefore an 883  $\Omega$  resistor (approximately). To change the trip value, follow the calculation procedures discussed above. As discussed in Section 3.4, the high-side overcurrent connector, JT3, cannot be left floating as the overcurrent fault will trip immediately when the high-side gate is actuated. If bench-top testing of the gate driver is required, it is acceptable to short this connector to the high-side source to prevent the overcurrent fault from tripping. The same phenomenon exists for the low-side, and it is acceptable to short the high-side source (low-side drain) to the low-side source for bench-top testing.

### 4.4.5 Miller Clamp

When a switch position is in the off state, high dV/dt in other switch positions can cause current flow through the Miller capacitance of a MOSFET and ultimately induce noise into the gate. To prevent false turn-on of the device, it is important that the gate driver has a low-impedance to the turn-off voltage when the device is off to ensure the gate of the MOSFET is held low. The Analog Devices ADuM4146 gate driver IC employed on this design features an integrated Miller clamp circuit. When the gate voltage drops below a 2 V internal reference, the Miller clamp latch is engaged, which is a low-impedance connection to the output-low voltage rail. In this configuration, the external turn-off resistor still controls the turn-off dynamics, and the gate driver has a lowimpedance connection to dissipate Miller charge even when a high-valued turn-off resistor is employed.

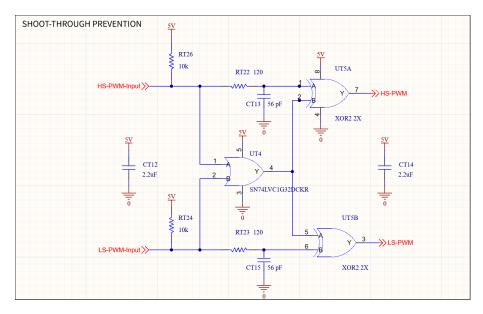

### 4.4.6 Interlock Protection

In a half-bridge circuit, commanding both channels on simultaneously short-circuits the bus and can cause extreme currents. While the overcurrent protection circuit discussed in 4.4.3 can prevent catastrophic damage this gate driver also includes circuitry intended to prevent both channels from being commanded on simultaneously. This interlock protection, also commonly referred to as shoot-through or anti-overlap protection, applies an XOR logic gate to the two input signals, preventing either output from going high if both signals are commanded on simultaneously, as shown in Table 10. This can help with noise rejection if noise causes one of the commanded signals to flip and it can help prevent issues from a faulty controller. Notably, this protection should not be relied upon for generating dead time. The implemented interlock protection circuit is shown in Figure 23.

**LS PWM HS PWM**  $V_{GS,HS}$  $V_{GS,LS}$ L L L L L Н L Н

Table 10: Interlock protection logic table

$H = High \mid L = Low$

Figure 23: Interlock prevention circuit

### 4.5 Soft Shutdown

When an overcurrent fault occurs, hard turn-off of the device (i.e. turning the device off normally) can induce large voltage overshoots due to the enormous di/dt event. To ensure the device voltage does not exceed safe operating area, the Analog Devices ADuM4146 includes an integrated soft shutdown feature. When the overcurrent fault is detected, a secondary N-channel MOSFET is used to shutdown the device. The second MOSFET has a resistance approximately 35 times more resistive than the normal turn-off MOSFET. Using this approach turns the power device off in a controlled manner to reduce the chance of an overvoltage spike.

## **4.6 Timing Definitions**

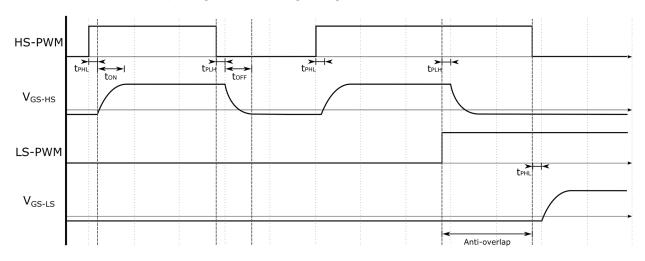

Table 2 provides various timing parameters to indicate the propagation delays of the gate driver. These timing parameters are shown visually in Figure 24 for the gate signals.

Figure 24: Gate timing diagram

### 4.7 Thermistor Feedback

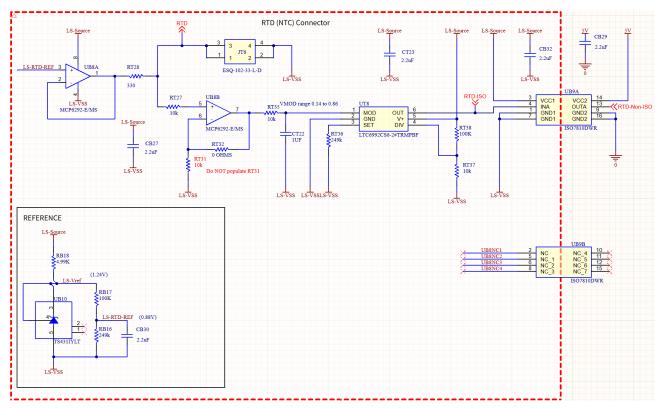

The resistance measurement of the XM3 power module's NTC thermistor is available on the input connector (*JT4*) of the gate driver as a differential pair on pins 9 and 10 (see Section 3.1). The thermistor resistance is converted to a PWM signal with varying duty cycle using the circuit shown in Figure 25. The NTC thermistor measurement circuit is attached to the low-side gate drive channel, and a digital isolator is used to transmit the duty cycle-encoded signal back to the primary side of the driver. For this reason, the NTC signal does not need any additional isolation and can be included in the same ribbon cable as the rest of the gate driver's signals.

Figure 25: Thermistor resistance to duty cycle conversion circuit

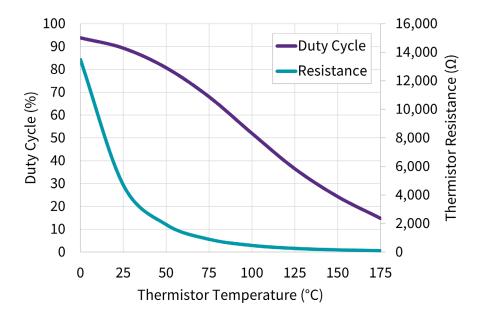

The temperature to duty cycle relationship of the thermistor is shown in Figure 26 and the corresponding numerical values are shown in Table 11. The duty cycle-encoded signal is transmitted at 50 kHz. On the controller side, the duty cycle-encoded signal can be interpreted by directly measuring the duty cycle using edge detection or the signal can be converted to an analog signal with a simple resistor-capacitor (RC) circuit. If using the analog approach, the RC circuit should have a long enough time constant to maintain a stable signal and then it can be measured with an analog-to-digital converter (ADC). The temperature reported by the thermistor differs largely from the junction temperature of the SiC MOSFETs and should not be used as an accurate junction temperature measurement (see <u>PRD-08376</u>).

Figure 26: Relationship between thermistor temperature, thermistor resistance, and output duty cycle

**Thermistor Thermistor** Output Duty Cycle (%) Temperature (°C) Resistance  $(\Omega)$ 0 13,491 93.8 25 4,700 89.3 50 1,928 80.7 75 898 68.0 100 464 52.0 125 260 36.5 150 156 24.3 175 99 14.8

Table 11: Gate driver thermistor characteristics

### **4.8 Power Estimates**

The gate driver power required to drive a switch position at a target switching frequency is calculated using the equation below. The gate charge is dependent on the datasheets of the module being driven. Once the required gate driver power is calculated, the required input power can be calculated from the efficiency curves on the datasheet of the applicable power supply. This calculation is for one channel of the gate driver.

$$P_{SW} = Q_G \cdot f_{SW} \cdot \Delta V_{PS}$$

where

$P_{SW}$ : per channel gate driver power [W]

$Q_G$ : total gate charge [C]  $f_{SW}$ : switching frequency [Hz]

$\Delta V_{PS}$ : difference in isolated power supply voltage rails ( $V_{PS,HIGH} - V_{PS,LOW}$ ) [V]

This calculation can be manipulated to determine the maximum switching frequency possible with a gate driver and power module combination (with some margin). An example calculation for the <a href="CAB450M12XM3">CAB450M12XM3</a> power module and CGD1200HB2P-XM3 gate driver is demonstrated below.

$P_{SW}$ : 2 W (rated output power of the isolated power supplies on the gate driver)

$Q_G$ : 1300 nC (provided in CAB450M12XM3 datasheet)

$V_{PS,HIGH}$ : 15 V (default positive output voltage of the isolated power supply)

$V_{PS,LOW}$ : -4 V (default negative output voltage of the isolated power supply)

$\Delta V_{PS}$ : 19 V (V<sub>PS,HIGH</sub> - V<sub>PS,LOW</sub>)

$$f_{SW} \le \frac{2 W}{1300 nC \cdot 19 V} \to f_{SW} \le 80 \text{ kHz}$$

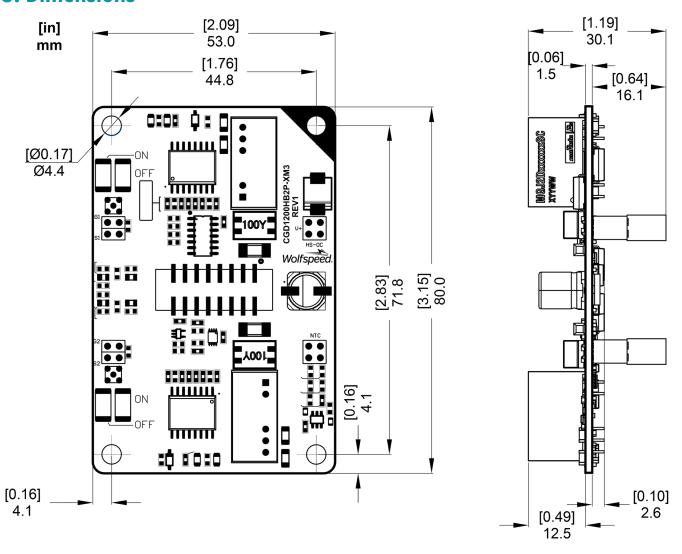

## 5. Dimensions

Figure 27: Dimensions of the CGD1200HB2P-XM3 gate driver

# 6. Supporting Links and Tools

The following links provide additional information about gate drivers, XM power modules, and design tools for using power modules. Please navigate to the landing page for this design for additional links and support.

## **6.1 Evaluation Tools and Support**

- XM Module Product Family

- KIT-CRD-CIL17N-XM: Dynamic Performance Evaluation Board for the XM Modules

- KIT-CRD-CIL12N-XM3: Evaluation Tool for the XM3 Module Platform

- SpeedFit 2.0 Design Simulator™

- <u>Technical Support Forum</u>

- All Wolfspeed Gate Drivers

### **6.2 Dual Channel Gate Driver Board**

• CGD12HB00D: Differential Transceiver Daughter Board Companion Tool for Differential Gate Drivers

## **6.3 Application Notes**

- PRD-07128: XM Module Signal Pinout Clarification Guide

- PRD-09301: Gate Driver Design for SiC Power Modules

- PRD-04814: Design Options for Wolfspeed Silicon Carbide MOSFET Gate Bias Power Supplies

# **Revision History**

| Date           | Revision | Changes         |

|----------------|----------|-----------------|

| September 2025 | 1        | Initial Release |

### **IMPORTANT NOTES**

### **PURPOSES AND USE**

Wolfspeed, Inc. (on behalf of itself and its affiliates, "Wolfspeed") reserves the right in its sole discretion to make corrections, enhancements, improvements, or other changes to the board or to discontinue the board.

THE BOARD DESCRIBED IS AN ENGINEERING TOOL INTENDED SOLELY FOR LABORATORY USE BY HIGHLY QUALIFIED AND EXPERIENCED ELECTRICAL ENGINEERS TO EVALUATE THE PERFORMANCE OF WOLFSPEED POWER SWITCHING DEVICES. THE BOARD SHOULD NOT BE USED AS ALL OR PART OF A FINISHED PRODUCT. THIS BOARD IS NOT SUITABLE FOR SALE TO OR USE BY CONSUMERS AND CAN BE HIGHLY DANGEROUS IF NOT USED PROPERLY. THIS BOARD IS NOT DESIGNED OR INTENDED TO BE INCORPORATED INTO ANY OTHER PRODUCT FOR RESALE. THE USER SHOULD CAREFULLY REVIEW THE DOCUMENT TO WHICH THESE NOTIFICATIONS ARE ATTACHED AND OTHER WRITTEN USER DOCUMENTATION THAT MAY BE PROVIDED BY WOLFSPEED (TOGETHER, THE "DOCUMENTATION") PRIOR TO USE. USE OF THIS BOARD IS AT THE USER'S SOLE RISK.

### **OPERATION OF BOARD**

It is important to operate the board within Wolfspeed's recommendations and environmental considerations as described in the Documentation. Exceeding specified ratings (such as input and output voltage, current, power, or environmental ranges) may cause property damage. If you have questions about these ratings, please contact Wolfspeed prior to connecting interface electronics (including input power and intended loads). Any loads applied outside of a specified output range may result in adverse consequences, including unintended or inaccurate evaluations or possible permanent damage to the board or its interfaced electronics. Please consult the Documentation prior to connecting any load to the board. If you have any questions about load specifications for the board, please contact Wolfspeed at forum.wolfspeed.com for assistance (and please rely only on forum responses from responders identified as Wolfspeed employees).

Users should ensure that appropriate safety procedures are followed when working with the board as serious injury, including death by electrocution or serious injury by electrical shock or electrical burns can occur if you do not follow proper safety precautions. It is not necessary in proper operation for the user to touch the board while it is energized. When devices are being attached to the board for testing, the board must be disconnected from the electrical source and any bulk capacitors must be fully discharged. When the board is connected to an electrical source and for a short time thereafter until board components are fully discharged, some board components will be electrically charged and/or have temperatures greater than 50° Celsius. These components may include bulk capacitors, connectors, linear regulators, switching transistors, heatsinks, resistors and SiC diodes that can be identified using a board schematic. Users should contact Wolfspeed for assistance if a board schematic is not included in the Documentation or if users have questions about a board's components. When operating the board, users should be aware that these components will be hot and could electrocute or electrically shock the user. As with all electronic evaluation tools, only qualified personnel knowledgeable in handling electronic performance evaluation, measurement, and diagnostic tools should use the board.

### **USER RESPONSIBILITY FOR SAFE HANDLING AND COMPLIANCE WITH LAWS**

Users should read the Documentation and, specifically, the various hazard descriptions and warnings contained in the Documentation, prior to handling the board. The Documentation contains important safety information about voltages and temperatures.

Users assume all responsibility and liability for the proper and safe handling of the board. Users are responsible for complying with all safety laws, rules, and regulations related to the use of the board. Users are responsible for (1) establishing protections and safeguards to ensure that a user's use of the board will not result in any property damage, injury, or death, even if the board should fail to perform as described, intended, or expected, and (2) ensuring the safety of any activities to be conducted by the user or the user's employees, affiliates, contractors, representatives, agents, or designees in the use of the board. User questions regarding the safe usage of the board should be directed to Wolfspeed at <a href="forum.wolfspeed.com">forum.wolfspeed.com</a> (but please rely only on forum responses from responders identified as Wolfspeed employees).

In addition, users are responsible for:

- compliance with all international, national, state, and local laws, rules, and regulations that apply to the handling or use of the board by a user or the user's employees, affiliates, contractors, representatives, agents, or designees.

- taking necessary measures, at the user's expense, to correct radio interference if operation of the board causes interference with radio communications. The board may generate, use, and/or radiate radio frequency energy, but it has not been tested for compliance within the limits of computing devices pursuant to Federal Communications Commission or Industry Canada rules, which are designed to provide protection against radio frequency interference.

- compliance with applicable regulatory or safety compliance or certification standards that may normally be associated with other products, such as those established by EU Directive 2011/65/EU of the European Parliament and of the Council on 8 June 2011 about the Restriction of Use of Hazardous Substances (or the RoHS 2 Directive) and EU Directive 2002/96/EC on Waste Electrical and Electronic Equipment (or WEEE). The board is not a finished end product and therefore may not meet such standards. Users are also responsible for properly disposing of a board's components and materials.

### **NO WARRANTY**

THE BOARD IS PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, INCLUDING BUT NOT LIMITED TO ANY WARRANTY OF NON-INFRINGEMENT, MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE, WHETHER EXPRESS OR IMPLIED. THERE IS NO REPRESENTATION THAT OPERATION OF THIS BOARD WILL BE UNINTERRUPTED OR ERROR FREE.

### **LIMITATION OF LIABILITY**

IN NO EVENT SHALL WOLFSPEED BE LIABLE FOR ANY DAMAGES OF ANY KIND ARISING FROM USE OF THE BOARD. WOLFSPEED'S AGGREGATE LIABILITY IN DAMAGES OR OTHERWISE SHALL IN NO EVENT EXCEED THE AMOUNT, IF ANY, RECEIVED BY WOLFSPEED IN EXCHANGE FOR THE BOARD. IN NO EVENT SHALL WOLFSPEED BE LIABLE FOR INCIDENTAL, CONSEQUENTIAL, OR SPECIAL LOSS OR DAMAGES OF ANY KIND, HOWEVER CAUSED, OR ANY PUNITIVE, EXEMPLARY, OR OTHER DAMAGES. NO ACTION, REGARDLESS OF FORM, ARISING OUT OF OR IN ANY WAY CONNECTED WITH ANY BOARD FURNISHED BY WOLFSPEED MAY BE BROUGHT AGAINST WOLFSPEED MORE THAN ONE (1) YEAR AFTER THE CAUSE OF ACTION ACCRUED.

### INDEMNIFICATION

The board is not a standard consumer or commercial product. As a result, any indemnification obligations imposed upon Wolfspeed by contract with respect to product safety, product liability, or intellectual property infringement do not apply to the board.