## CONTENTS

Specifications and Design Challenges

- Topology, Power Components Selection

- Magnetics Design and PCB Layout Considerations

- 4 Test Results

— Summary

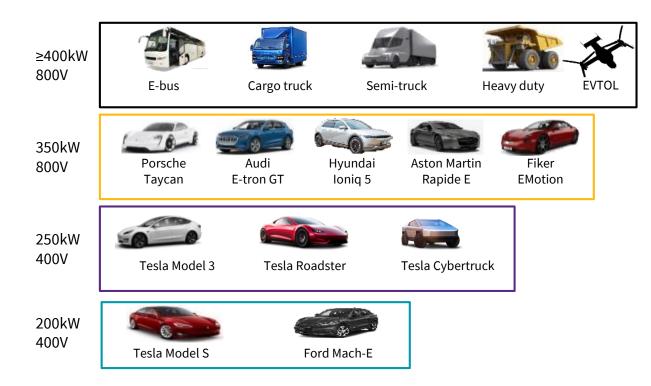

#### TREND FOR EV DC FAST CHARGING: INCREASED POWER AND VOLTAGE

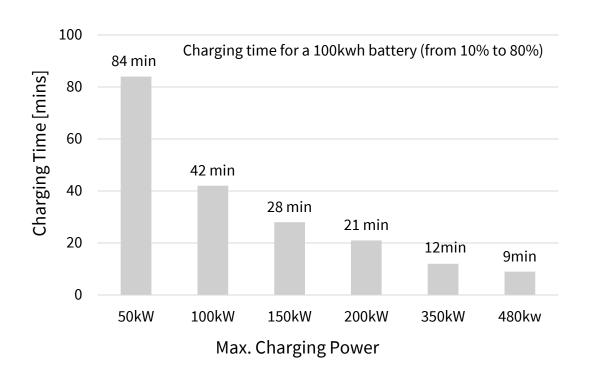

## Charging Power vs. Charging Time

• Max. Charging Power for Selected EV from Major Automakers

- **EV owners**: Resolve mileage anxiety, better charging experience

- Automakers: Selling point for mainstream and high-end cars

- Charging point operators: Shorter charging time, higher turn over, more cashflow

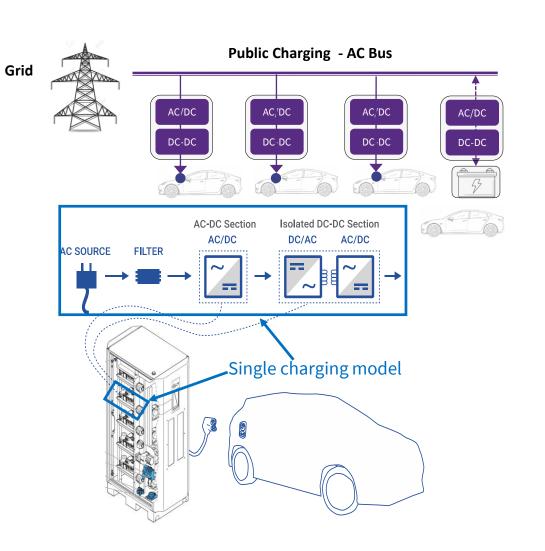

## DC FAST CHARGER – CHALLENGE AND TREND

#### **Trend**

- Very wide output voltage range: 200V-1000V

- High efficiency, high power density and competitive cost

- Increasing power level for each module: 15kW/20kW → 30kW, 40kW and 60kW

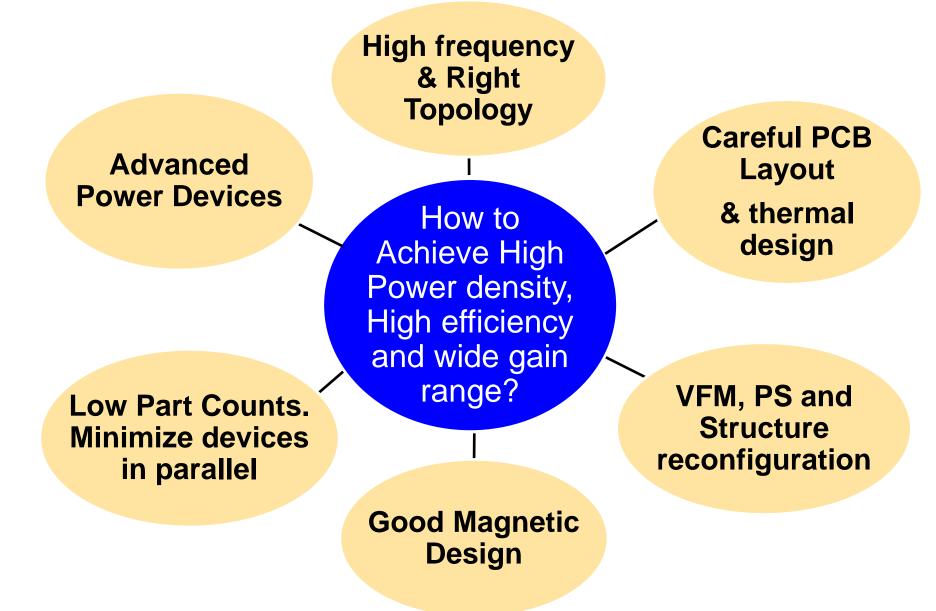

## HIGH POWER DENSITY, HIGH EFFICIENCY, WIDE VOLTAGE RANGE

## **TOPOLOGY SELECTION: 30KW-60KW BLOCKS | DCDC UNIDIRECTIONAL**

demarks and the Wolfspeed logo is a trademark of Wolfspeed, Inc.

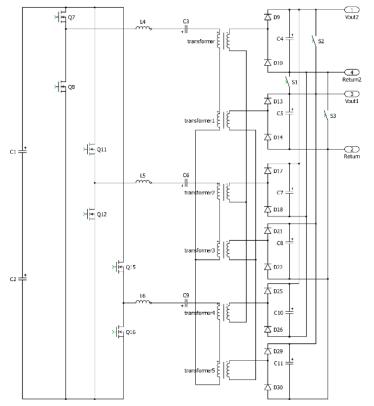

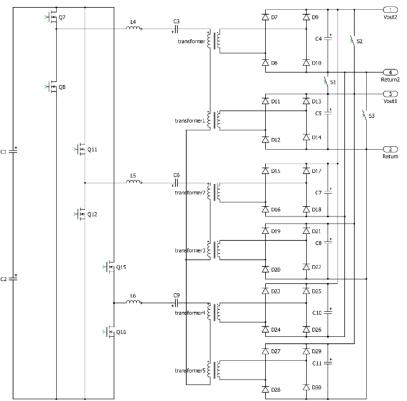

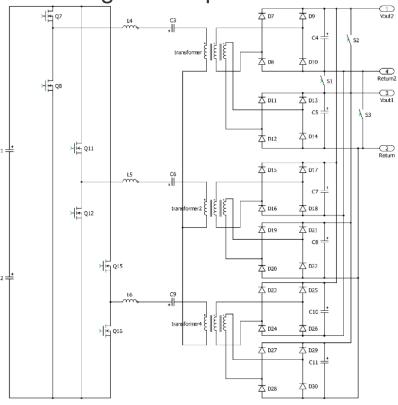

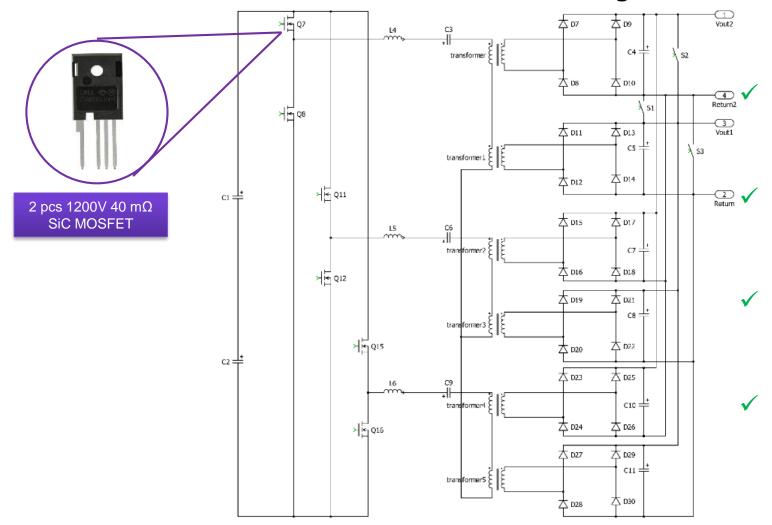

#### **TOPOLOGY SELECTION**

A

6 Transformers

Half Bridge for output rectifier

6 Transformers

Full Bridge for output rectifier

3 Transformers

Full Bridge for output rectifier

Current sharing concerns on Si output rectifiers in parallel; EMI concern due to large loop

Voltage sharing concerns

V/I sharing concerns

C is selected for 30kW; B will be considered for 60kW The output rectifier are equivalent to each other. The total current rating of output rectifier are same. Even we see 24 positions in B and C and 12 in A.

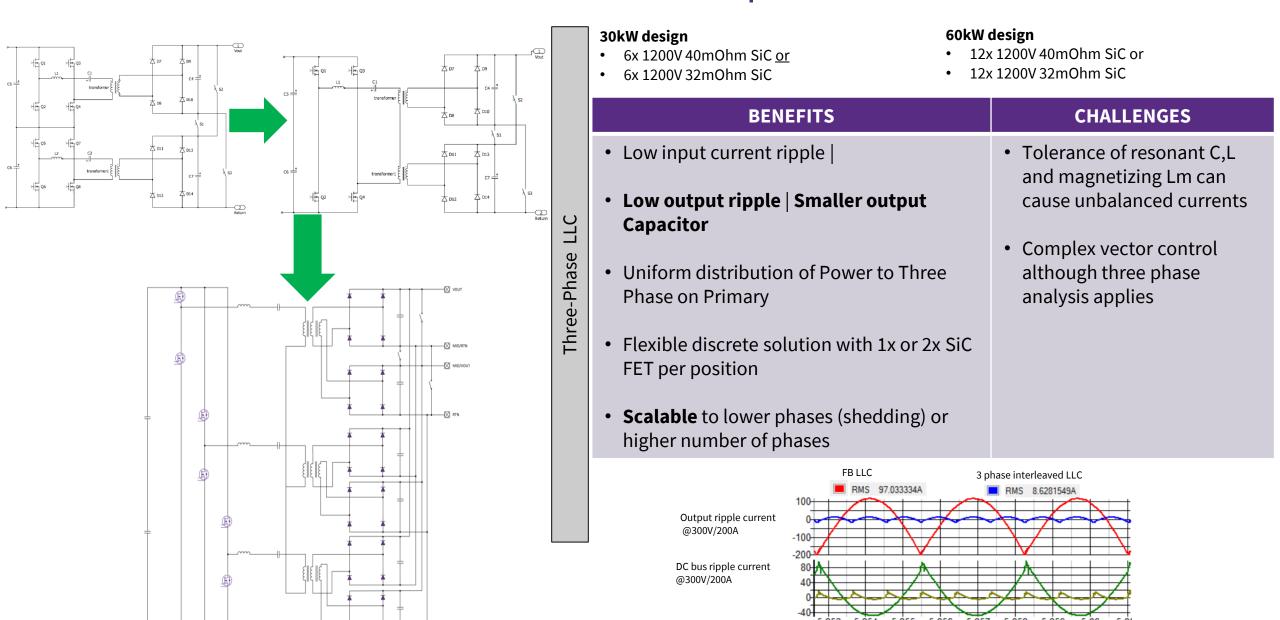

#### **TOPOLOGY SELECTION**

3phase output Bridge rectifier

Full Bridge output rectifier

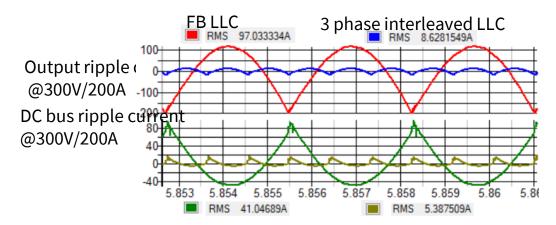

#### **OUTPUT CAPACITOR RIPPLE STRESS AND COMPONENTS SELECTION 60KW**

| Topology     | Condition           | Rms current<br>Output | Output Caps       | Rms current<br>Input | Input Caps       |

|--------------|---------------------|-----------------------|-------------------|----------------------|------------------|

| 3 phase Y-FB | 300V 200A<br>output | 8.6A                  | 630V 3uF *6       | 8A                   | 1100V 2uF *4     |

| FB-FB        | 300V 200A<br>output | 97A                   | 630V 4.7uF<br>*24 | 44A                  | 1100V 2uF<br>*14 |

Input & output ripple and the size of filtering caps are much smaller in 3 phase LLC. It helps to improve the eff and power density.

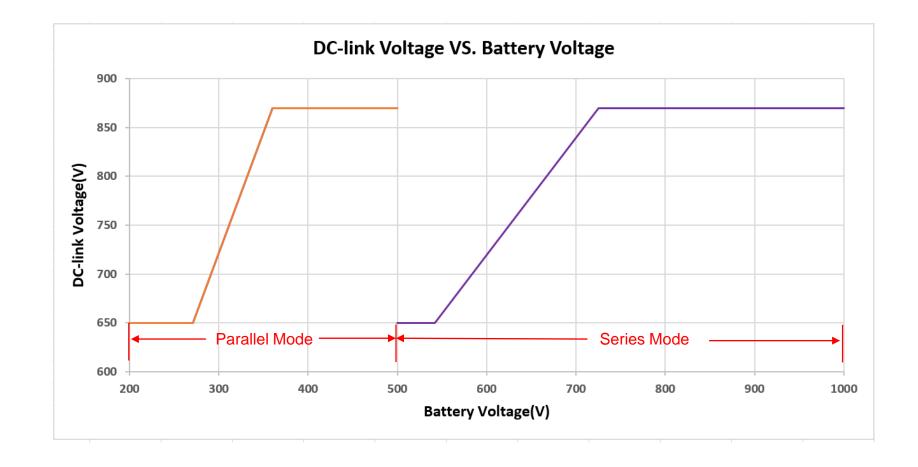

## **FLEXIBLE DC-LINK CONTROL**

Fr=180kHz Lr=7.5uH Cr=102nF Lm=30uH

## **POWER COMPONENTS SELECTION**

The DC link voltage is up to 870V. 65A max rms current.

C3M0040120K 1200V 40mohm SiC MOSFET is selected for primary MOSFET of LLC converter based on electrical stress and thermal design. 12 devices provide 60kW output.

#### Why SiC?

Fast switching and low switching losses for 1200V device. Enabling high-frequency switching

Smaller output capacitance, easier to achieve ZVS for LLC resonant converter

Less temperature dependence of Rdson and low conduction loss at high temperature

Low reverse recovery body diode enables reliability in case of hard-commutation

## **DESIGN CONSIDERATIONS – POWER TRANSFORMER**

## PARAMETERS AND PERFORMANCE COMPARISON – TX CORE MATERIAL

|                    | 3C95                                | 3C97                                | TPW33                               |

|--------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| ui                 | 3000                                | 3000                                | 3300                                |

| Bmax               | 530mT@ 25 °C<br>410mT@ 100 °C       | 550mT@ 25 °C<br>430mT@ 100 °C       | 520mT@ 25 °C<br>410mT@ 100 °C       |

| Pv(200mT/100kHz)   | 350kW/m3@ 25 °C<br>290kW/m3@ 100 °C | 320kW/m3@ 60 °C<br>380kW/m3@ 140 °C | 380kW/m3@ 25 °C<br>300kW/m3@ 100 °C |

| T_range optimized  | 25 °C-100 °C                        | 50 °C-150 °C                        | 25 °C-120 °C                        |

| Frequency<br>Range | <500kHz                             | <500kHz                             | <500kHz                             |

| Vendor             | Ferroxcube                          | Ferroxcube                          | TDG                                 |

• 3C97 is selected due to its wide temperature range for low power loss.

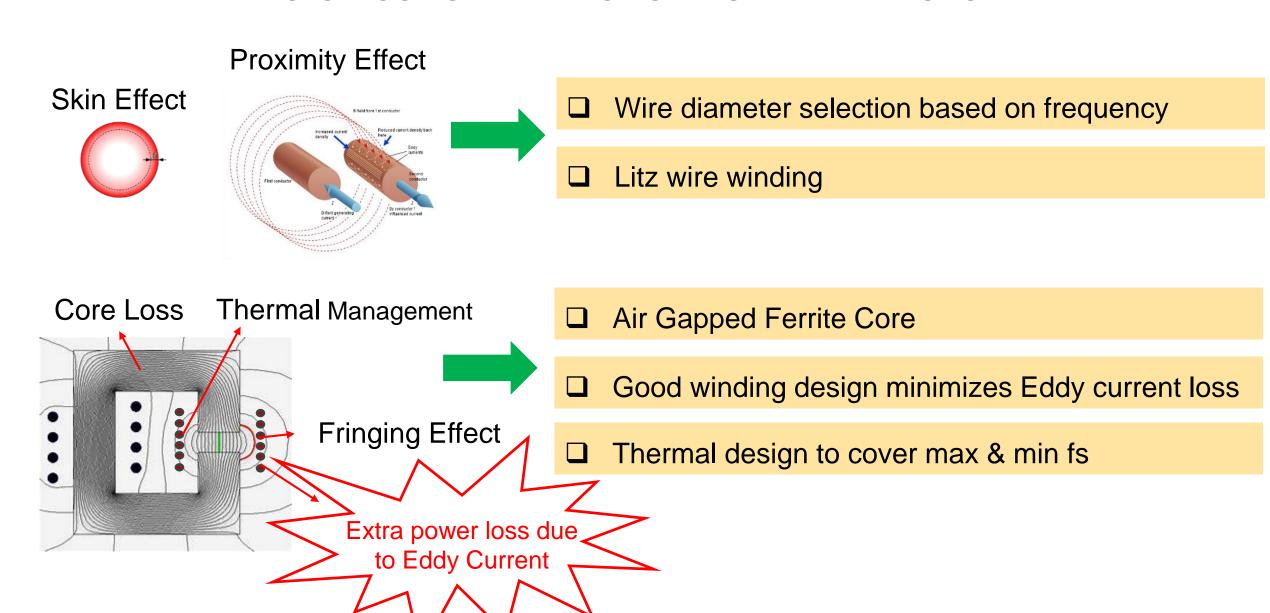

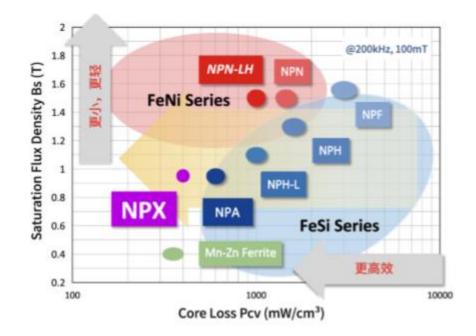

## **DESIGN CONSIDERATIONS – RESONANT CHOKE**

## **Proximity Effect**

#### Skin Effect

- ☐ Wire diameter selection based on frequency

- ☐ Litz wire winding

- NPX Powder Core instead or Air Gapped Ferrite

- ☐ Balance of Core Loss and Winding loss

- ☐ Low thermal resistance at system level

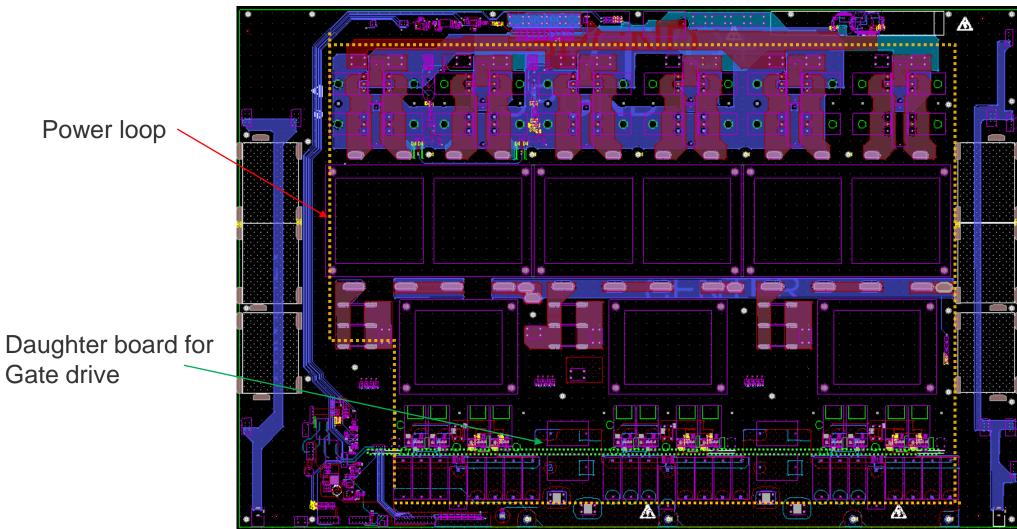

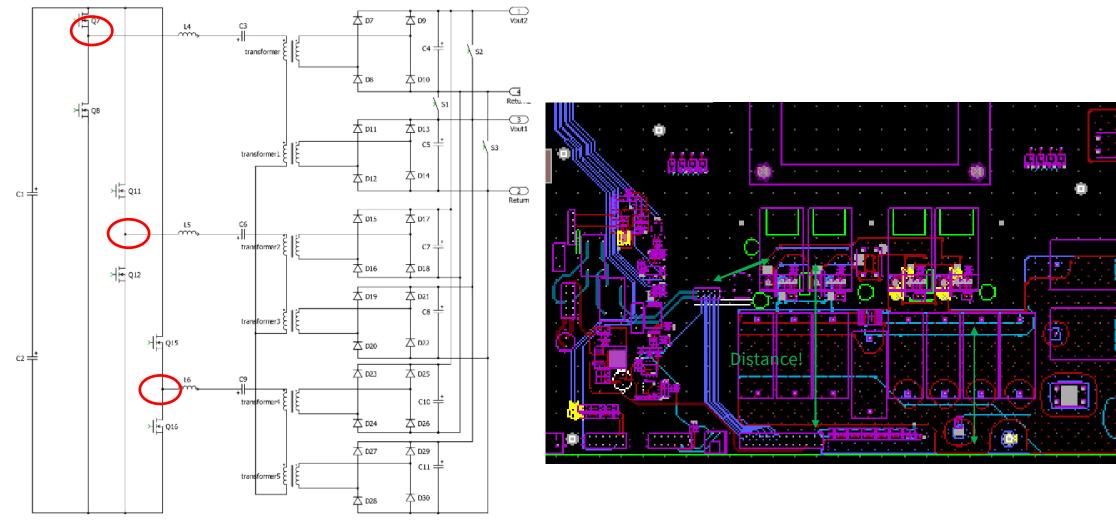

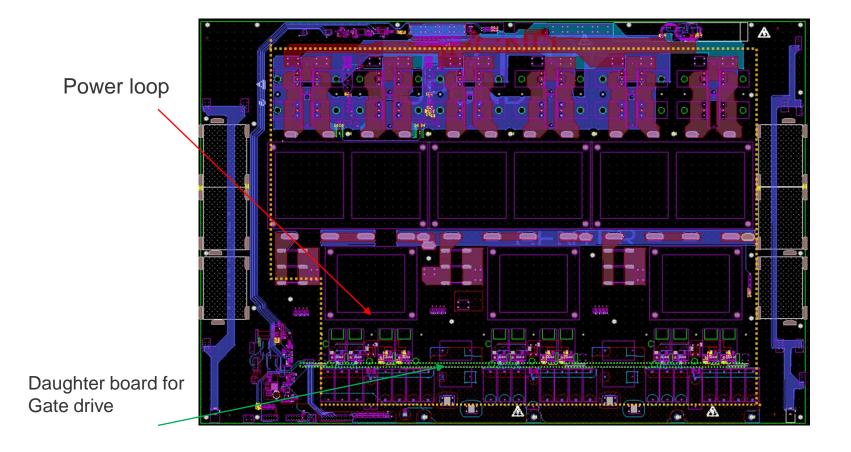

## **COMPONENTS PLACEMENT**

Avoid overlap between Gate, Gate drive circuit, bias power supply for Gate drive and the drain of the MOSFET.

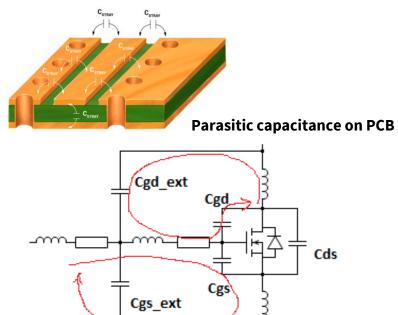

## **HIGH DV/DT TRACE/NODE**

- Keep the sensitive signals far away from the high dV/dt trace/nodes.

- Keep the sensitive signals far away from the high magnetic field such as resonant choke, power transformer.

- Small pad size of Drain nodes to reduce the coupling and parasitic capacitance

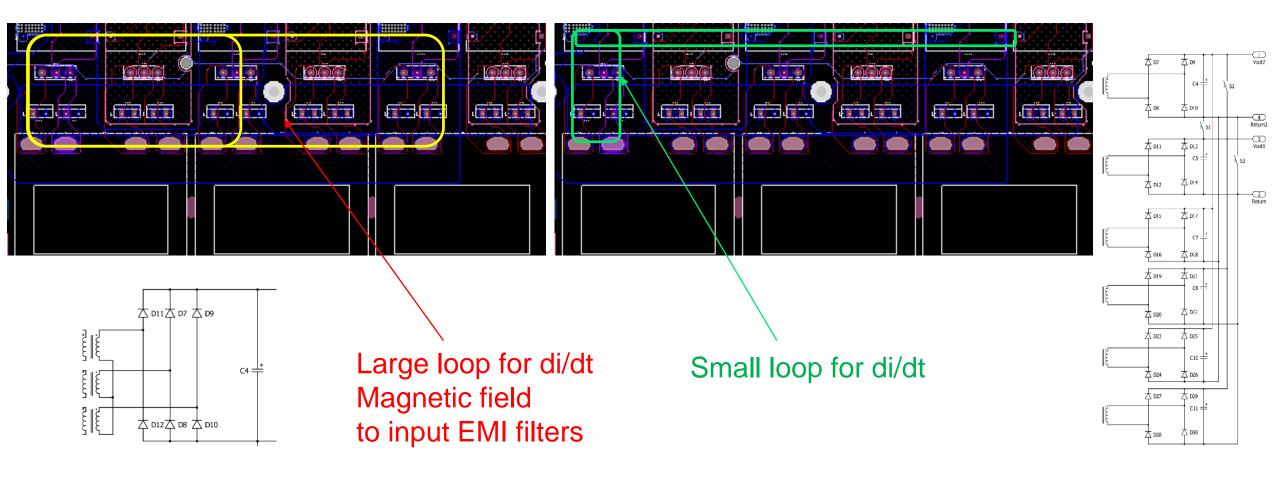

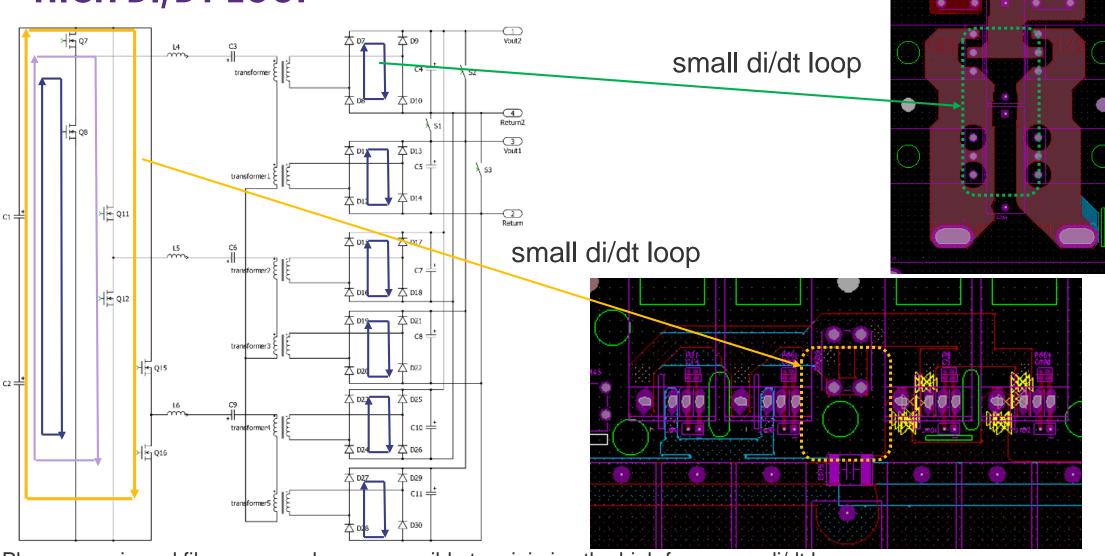

## **HIGH DI/DT LOOP**

- •Place ceramic and film caps as close as possible to minimize the high frequency di/dt loop.

- •Proper PCB layout of the power components to minimize the high frequency di/dt loop.

#### **COMPONENTS PLACEMENT**

Similar PCB design rules for SiC and Si → Avoid overlap between Gate+Gate-drive-circuit and the drain of MOSFET.

#### Consequences external Cgd:

- Not only higher switching loss

- Risk of gate oscillation

- EMI

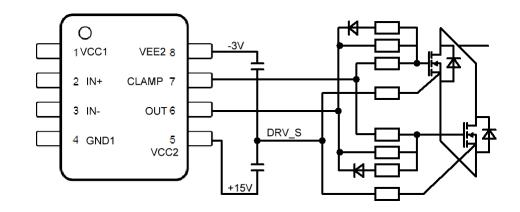

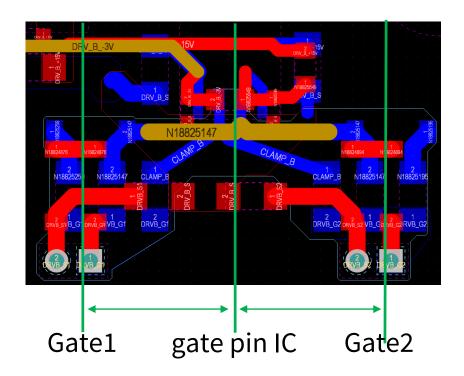

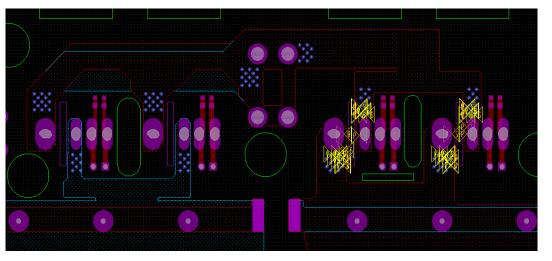

#### PCB LAYOUT FOR PARALLELED SIC MOSFET IN 60KW REFERENCE DESIGN

- Minimized the loop of gate drive and active miller clamp

- Symmetrical Gate and return paths

- Have resistors in both Gate and Kelvin-Source and close to the MOSFETs

- Add a small inductance to power source pin of the paralleled MOSFET to improve dynamic current sharing.

- Minimize stray inductance at drain

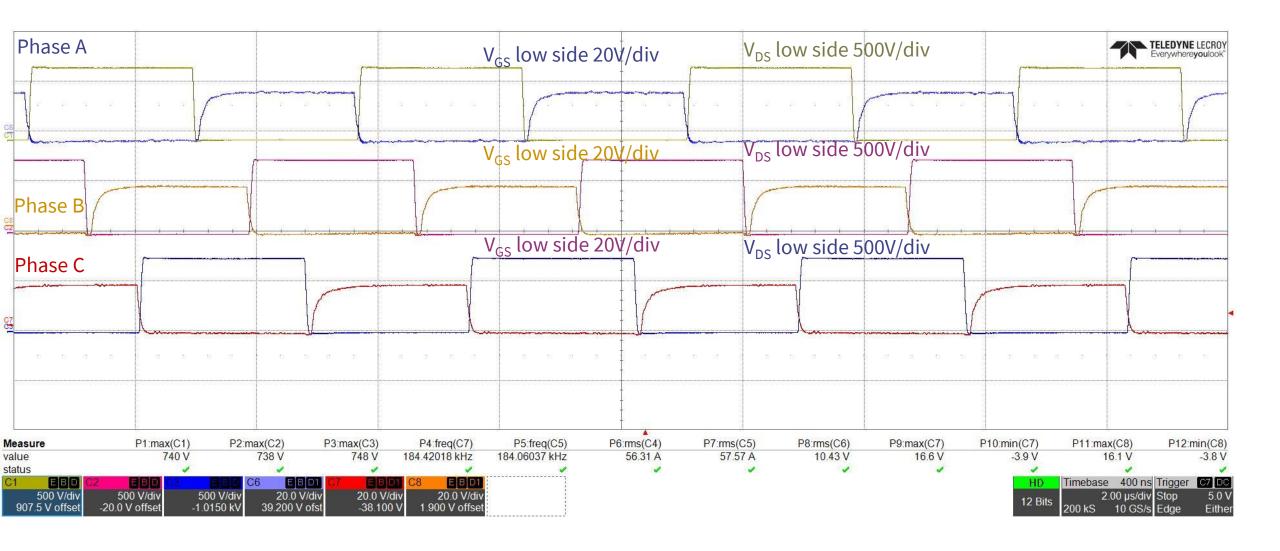

## **WAVEFORMS - 3PHASE INTERLEAVED - V<sub>GS</sub> V<sub>DS</sub>**

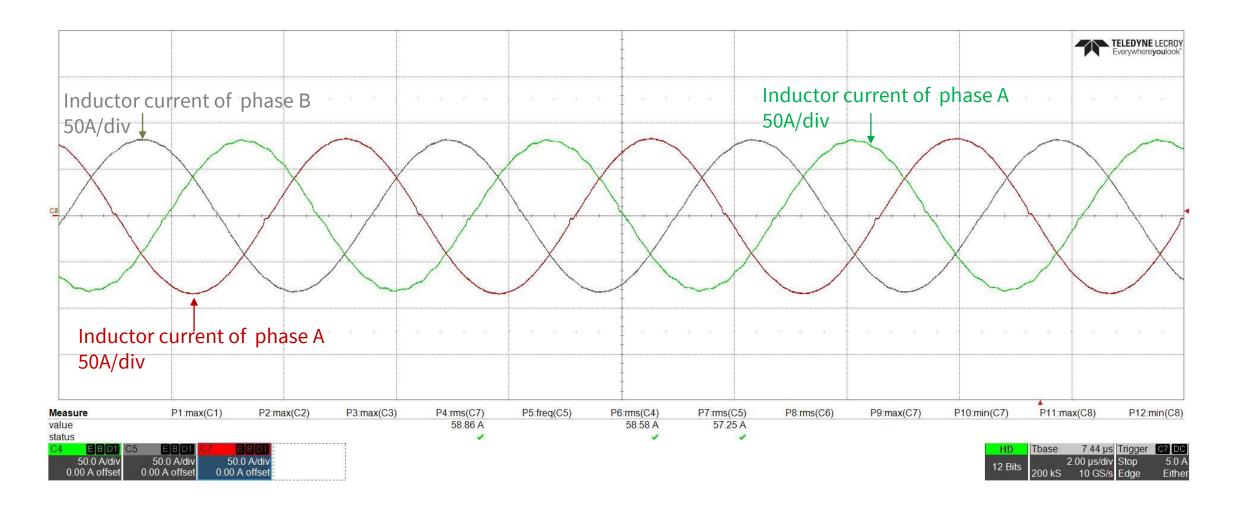

## **WAVEFORMS - 3PHASE INTERLEAVED - INDUCTOR CURRENT**

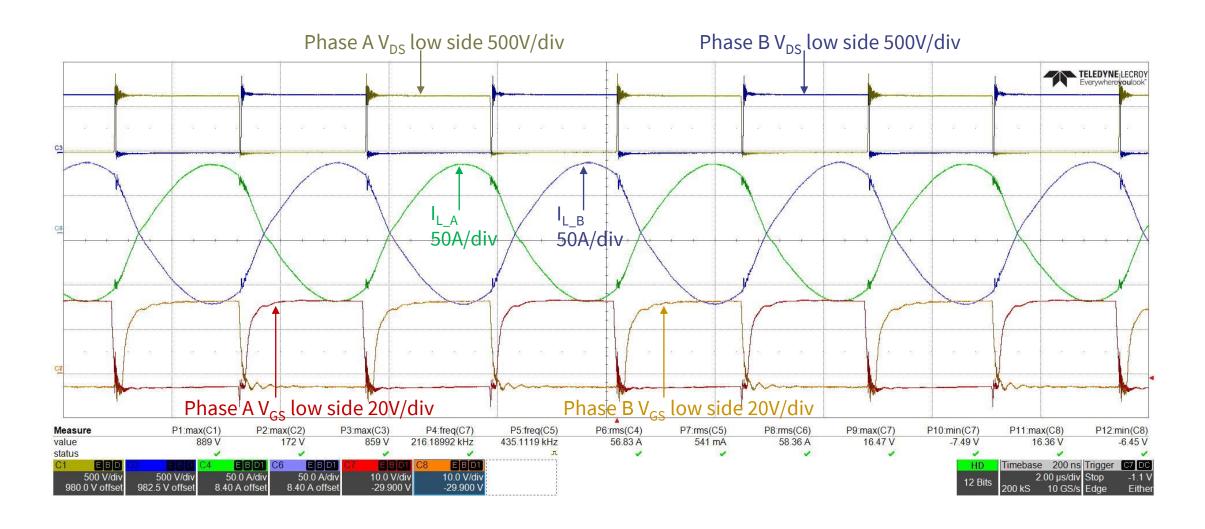

## **WAVEFORMS - FULL BRIDGE**

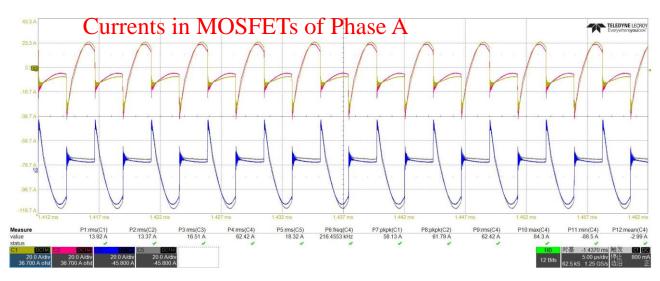

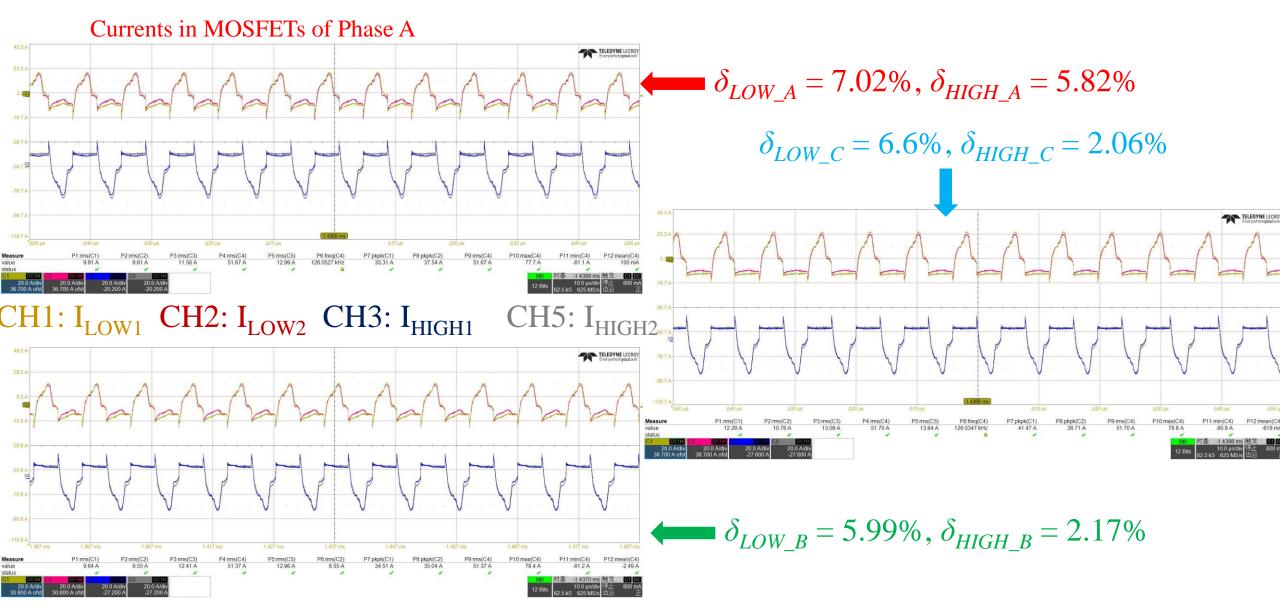

## 200V/26KW- CURRENT SHARING BETWEEN PARALLEL MOSFETS

The current unbalance rate  $\delta$  is calculated as:

$$\delta = \frac{\Delta I}{I_{avg}} \times 100\%$$

Where:

$\Delta I$  — Current difference between the two parallel MOSFETs

$I_{avg}$  —— Average current of the two parallel MOSFETs

$$\delta_{LOW\ A} = 2.02\%, \, \delta_{HIGH\ A} = 5.2\%$$

CH1: I<sub>LOW1</sub> CH2: I<sub>LOW2</sub> CH3: I<sub>HIGH1</sub> CH5: I<sub>HIGH2</sub>

$\delta_{LOW\ B} = 3.4\%, \, \delta_{HIGH\ B} = 1.88\%$

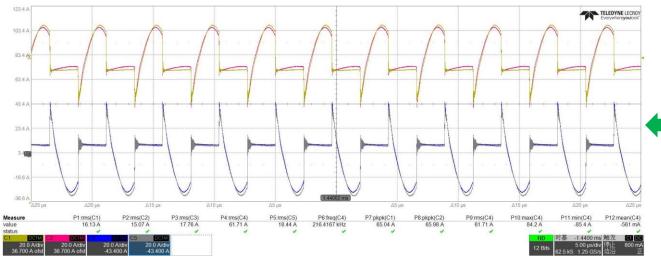

## 250V/50KW- CURRENT SHARING BETWEEN PARALLEL MOSFETS

Currents in MOSFETs of Phase B

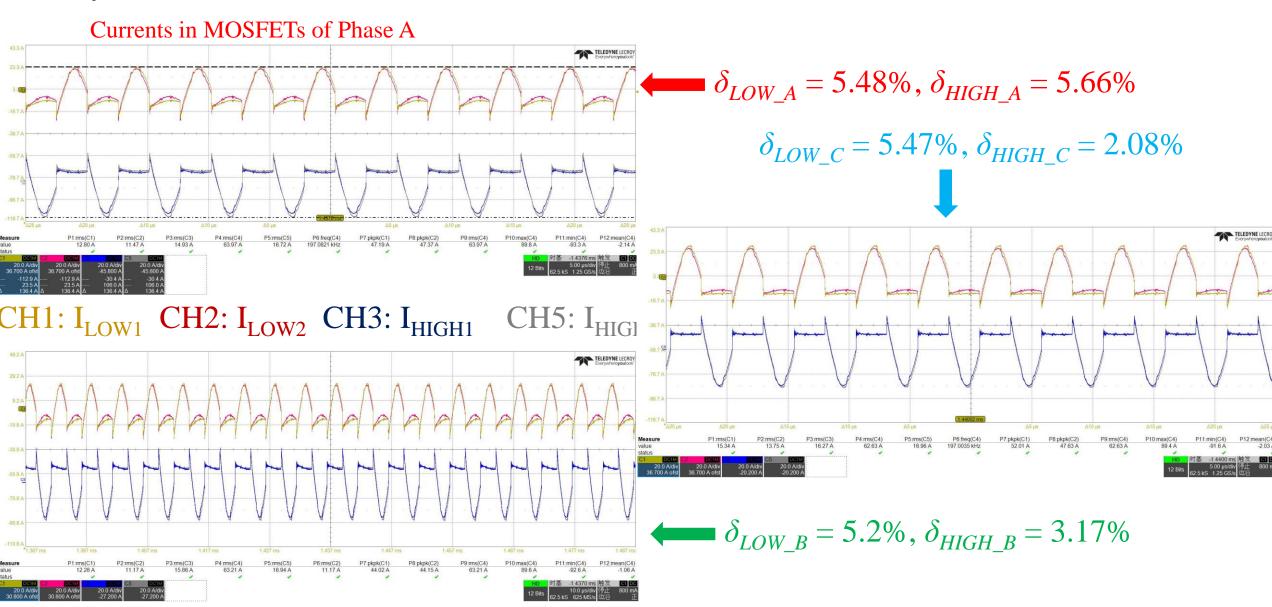

## 300V/60KW- CURRENT SHARING BETWEEN PARALLEL MOSFETS

Currents in MOSFETs of Phase B

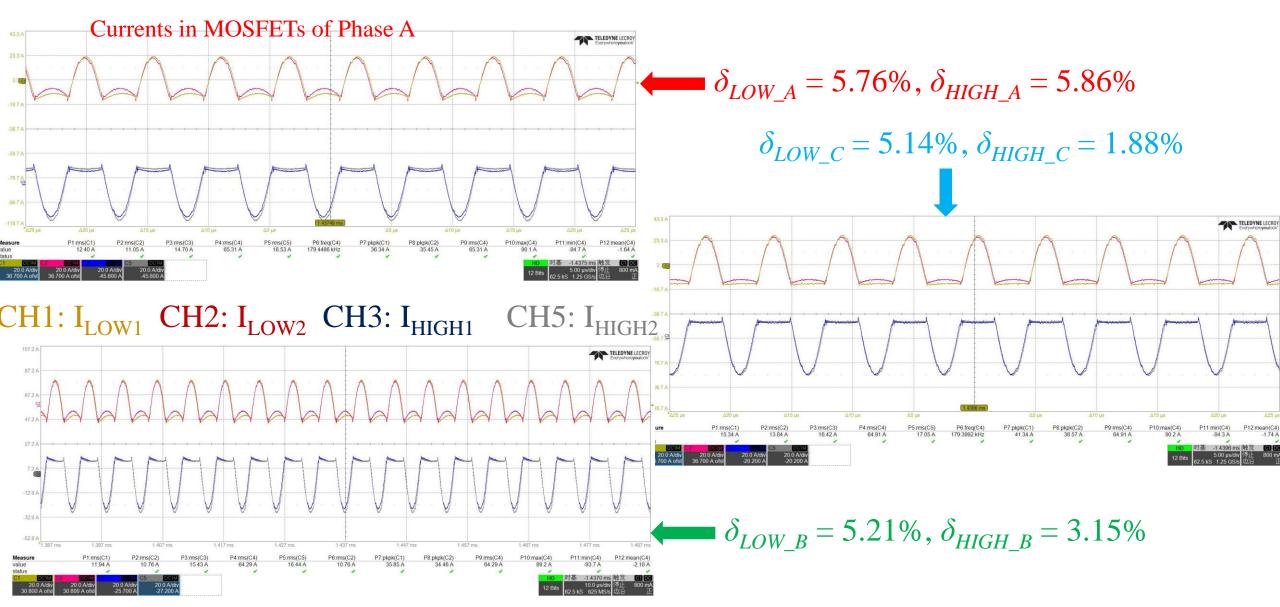

## 500V/58KW- CURRENT SHARING BETWEEN PARALLEL MOSFETS

Currents in MOSFETs of Phase B

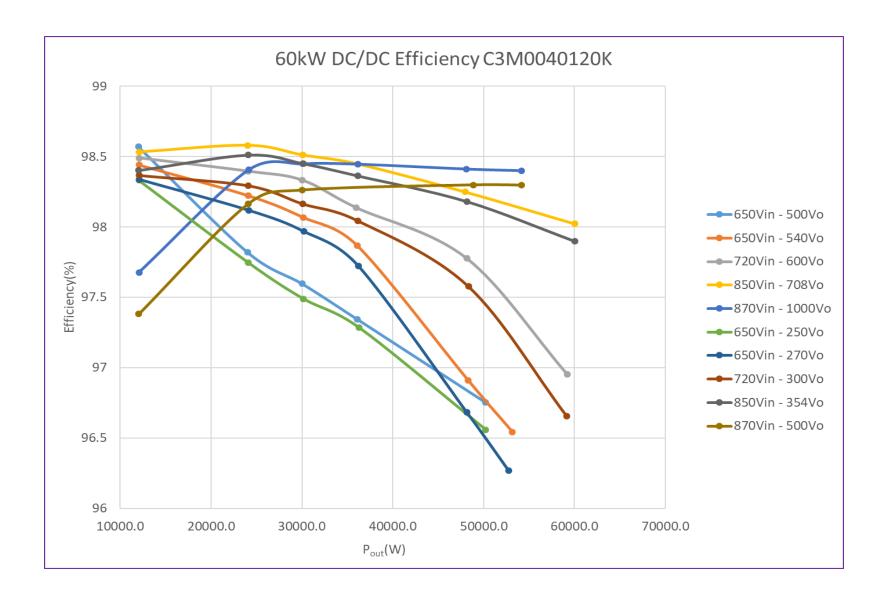

#### **EFFICIENCY TEST RESULT**

## THERMAL RESULTS (TESTED TJ < MAX TJ \*0.8 = 140 °C)

| Part Number                                   | Heatsink<br>Temp.                      | Rth (j-c)<br>(c/w) | Calculated<br>Power Loss<br>(watts) | '     | Calculated<br>Junction<br>Temp. | Max. Junction<br>Temp. | Comments |  |

|-----------------------------------------------|----------------------------------------|--------------------|-------------------------------------|-------|---------------------------------|------------------------|----------|--|

|                                               | 720Vdc Input, 300Vdc Output, full load |                    |                                     |       |                                 |                        |          |  |

| C3M0040120K<br>Q23                            | 85                                     | 0.46               | 33.2                                | 96.6  | 111.9                           | 175 °C                 | PASS     |  |

| 650Vdc Input, 200Vdc Output, full bridge mode |                                        |                    |                                     |       |                                 |                        |          |  |

| C3M0040120K<br>Q23                            | 85                                     | 0.46               | 47.5                                | 101.6 | 123.4                           | 175 °C                 | PASS     |  |

| 870Vdc Input, 500Vdc Output, full load        |                                        |                    |                                     |       |                                 |                        |          |  |

| C3M0040120K<br>Q23                            | 85                                     | 0.46               | 31                                  | 95.8  | 110.06                          | 175 °C                 | PASS     |  |

### **SUMMARY**

The value to get the low power loss from:

- C3M 1200V SiC MOSFET,

- the flexible control scheme

- proper PCB layout

## Below design targets are achieved:

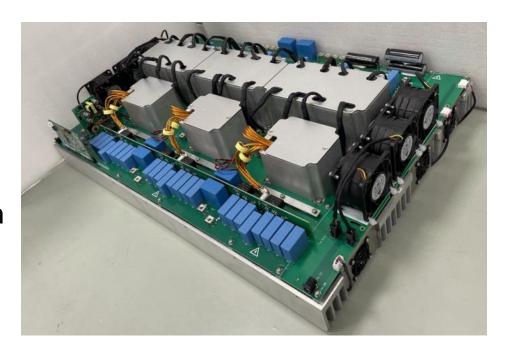

- ✓ Low parts counts, 12 pcs TO-247-4 1200V 40mohm SiC discrete MOSFETs to cover 60kW

- ✓ High Efficiency up to 98.5% for DC DC converter

- ✓ Wide battery voltage range 200Vdc-1000Vdc

- ✓ Good Current Sharing between phases and MOSFETs

## THANK YOU

# We harness the power of Silicon Carbide to change the world for the better